Other Parts Discussed in Thread: TPL0102-100, OPA333

Dear all,

I am designing an ultra low-power analog front-end for a sensor interface that will use a 12b ADC. In order to maximize the ADC DR, I need a PGA that will use an opa333 + a 2-channels digital potentiometer TPL0102-100 in the feedback path in a typical non-inverting amplifier configuration. I have 2 options:

O1) Using 1 channel of the TPL0102-100 in Voltage Divider mode

O2) Using 2 channels of the TPL0102-100 in Rheostat mode

I have 4 questions:

A) Which option is best for gain accuracy? Being the gain dependent on Resistance ratios, is it better the ratio of Rhw/Rwl (O1) or rather R1/R2 (O2)? Is it correct stating that with O1 I should expect accuracy better than 0.5/256=2mV/V whereas for O2 it will be 2/256=7.8mV/V?

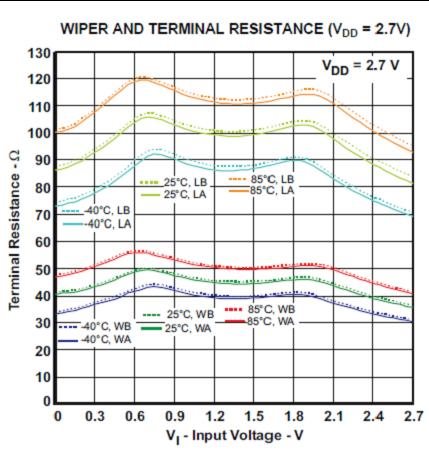

B) Which option is best for non linear distortion considering I will use a 3.3V supply with about 3Vpk-pk of output signal swing? In voltage mode I see 0.03% THD (for only 1Vrms) which would give max 70dB DR which means I would eat up part of my 12b ADC DR (ideally 74dB). Is that correct? How about the rheostat mode non linearity?

C) O1 will give me a worse case bandwidth of about BW=1/(2*pi*50kOhm*(10+16)pF)~122kHz whereas O2 gives BW=1/(2*pi*100kOhm*(10+22)pF)~50kHz. Can you confirm that both options would be ok as far as BW having a 2kHz max signal frequency and sampling @ 8kHz?

D) Is there a PSPICE model available for the TPL0102-100 somewhere or what is the fastest way to test it around an opamp?

I look forward to hearing from you.

Best Regards,

Vito