Part Number: LSF0108

Hi all,

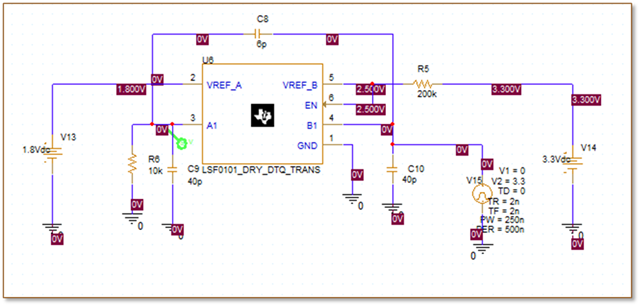

In our customer's 3.3 V to 1.8 V conversion line, overshoot that did not occur in the prototype occurred in the second prototype.The left is the signal waveform with no problem, and the right is the waveform with overshoot.

The phenomenon follows LSF0108. Also, there is a difference in marking between these devices.

1) What is the difference between them?

2) Please tell me the specific cause and countermeasures.We, the distributor, conducted a simulation and found that there is a difference due to capacity. For this phenomenon, the peak voltage is lowered by placing a series resistor, but the constant cannot be determined.

3) Is this understanding correct? Is the countermeasure for this problem to place a series resistor as a way to suppress the rise time? If so, what is the constant of the resistor?

4) Please let me know if there is another countermeasure.

Best Regards,

Ryusuke