Part Number: TCAN4550EVM

Hi team,

My customer is testing TCAN4550EVM.

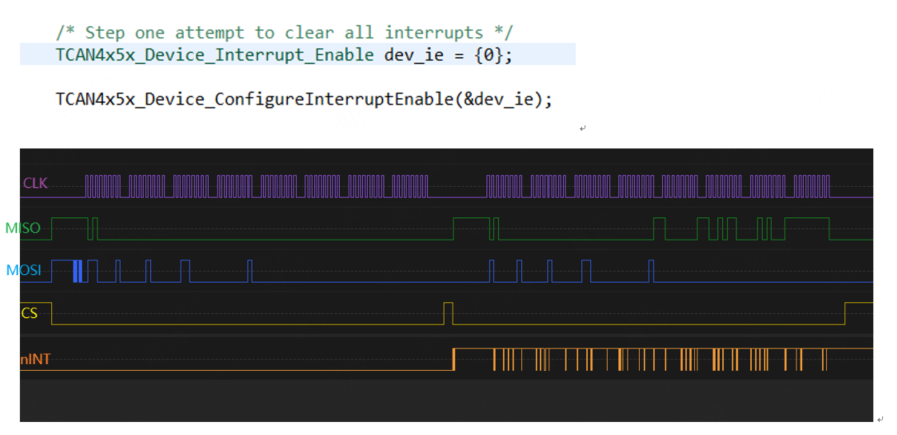

They use API TCAN4x5x_Device_ConfigureInterruptEnable(&0) to disable all interrupt, but nINT still will action. And they read registers 0820h and 0830h are not all 0.

Could you help explain why interrupt can't be disabled by this API?

Thanks,

Severi