Part Number: TCAN4551-Q1

Other Parts Discussed in Thread: TCAN4550,

Hi experts,

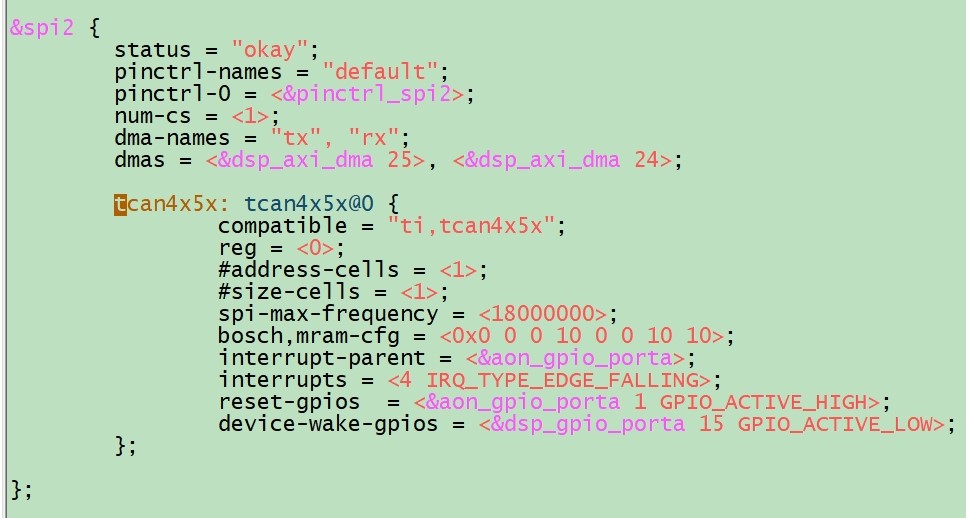

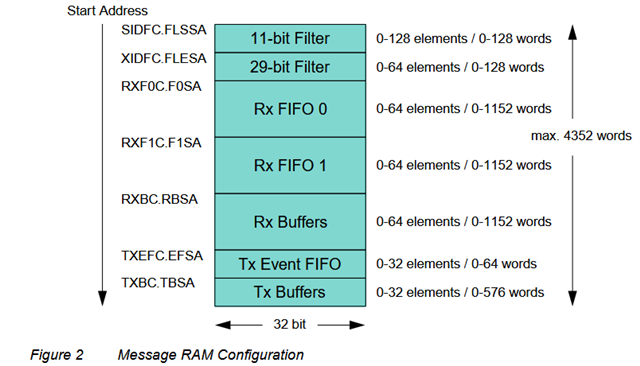

customer will meet the write: No buffer space available error when linux and PC exchange message every 100ms through TCAN4551. Below is customer X5M Linux platform dts configuration. the SPI speed is 18MHz. Is there any problem?