Part Number: TCA9543A

Due to the SoC GPIO limitation, the two I2C pins are also used as boot strap pins. During SoC startup, these I2C pins must be held low initially.

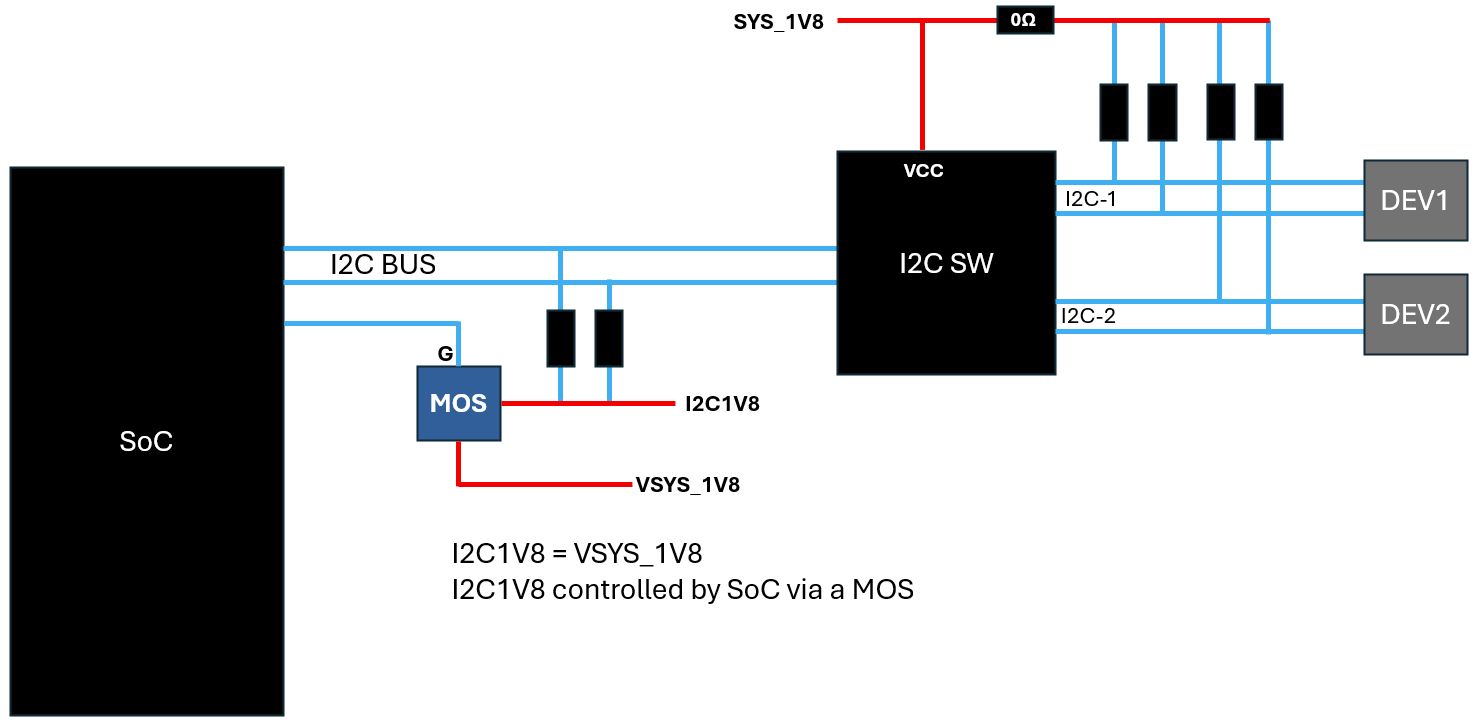

Therefore, we added a MOS circuit to control the power-up timing of the I2C pull-up voltage. In other words, the SoC enables the MOSFET gate only after the system has fully booted, which then provides 1.8V to the I2C pull-up power.

Without this sequence control, the SoC would fail to initialize properly.

The current connection between the SoC and the I2C switch is shown in the diagram. The issue we are encountering is that, under normal operation, if we perform a software reset (SW RST) on the SoC alone, the SoC fails to boot successfully afterward.

After analysis, this behavior appears to be directly related to the I2C switch. When we cut off the VCC power of the I2C switch, the SoC boots normally.

We would like to clarify a few questions:

-

If the I2C pull-up power of the SoC and the slave side are at the same voltage level, can we omit the pull-up resistors on the slave side?

-

Will the I2C signals on the slave side leak or propagate to the master side?

-

Why is it that when we turn off the pull-up power on the slave side (while keeping the I2C switch VDD powered), we cannot access the TCA9543A via I2C commands?