Hi team,

My customer would like to make sure behavior of RX_CTRL signal when IFG(Interframe Gap) is shorter than minimum required time, which is 96ns(=12 clk x 8ns/clk).

[Background]

They're performing ethernet communication via switching hub. Each master and slave equipment uses DP83867IR for PHY.

When transmitting data which exeeds max payload size of ethernet frame, the frame is divided. For this example, the frame is divided into 3 frames.

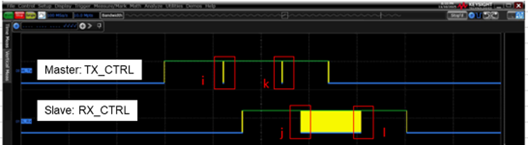

Sometime, the data frame transmitted from HUB excibits IFG, which is shorter than minimum required time(96ns). In this case, RX_CTRL signal of DP83867IR at Rx side toggles High/Low, indicating receive error. They repeat transmit data periodicaly(roughly several 10 ms) and the issue occurs about a few minutes later.

[Waveforms]

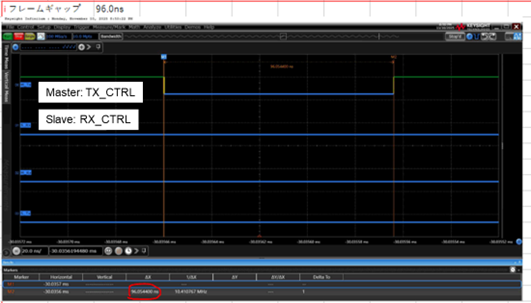

IFG of Tx side(above i and k) was about 96ns.

Above i: IFG of Tx side was about 96ns

Above k: IFG of Tx side was about 95.7ns

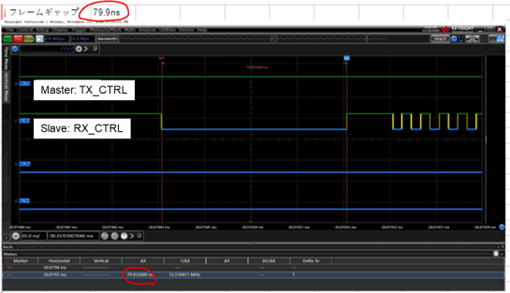

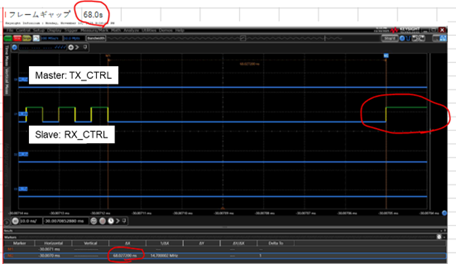

When the issue occurs, IFG(above j and l) was clearly less than 96ns.

Above j: IFG of Rx side was 79.9ns.

Above l: IFG of Rx side was 68.0ns.

[Questions]

- When IFG is shorter than specified minimum value(96ns), RX_CTRL signal toggles High/Low like above waveforms while receiving data frame. Is this expected behavior?

- Is there any register which can change minimum required IFG in the PHY?

- For RX side, second and third IFG were 68ns, but when receiving theird frame, RX_CTRL signal sticked to High.

Is this expected behavior?

Best regards,

Shota Mago