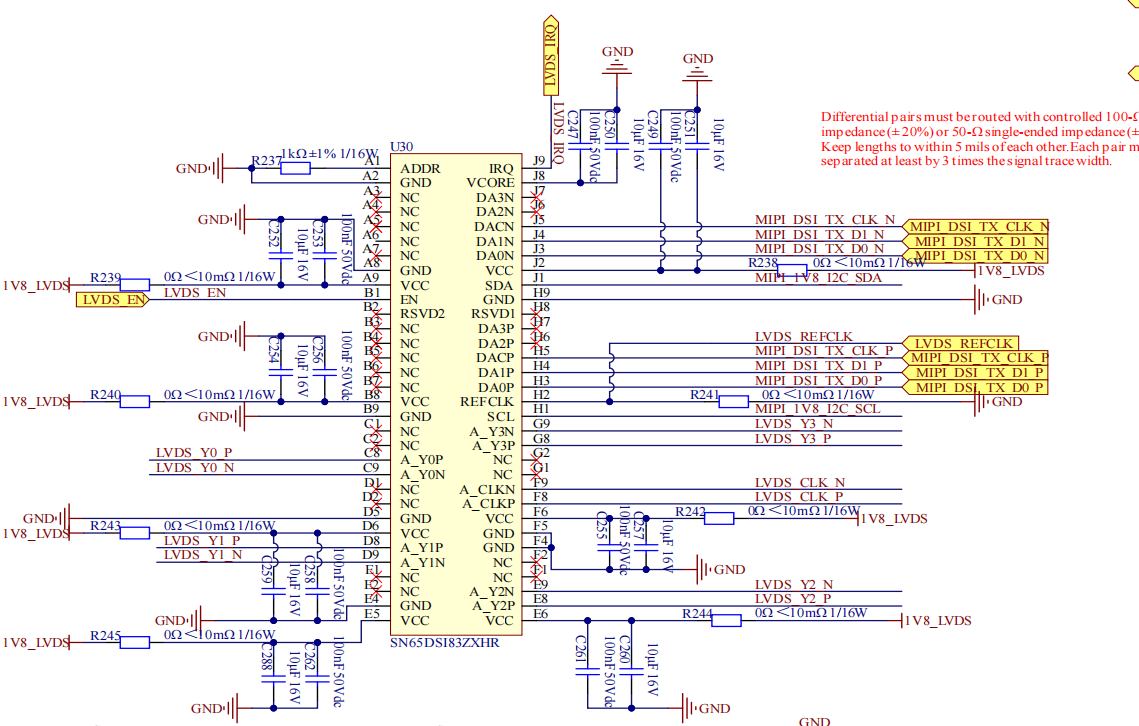

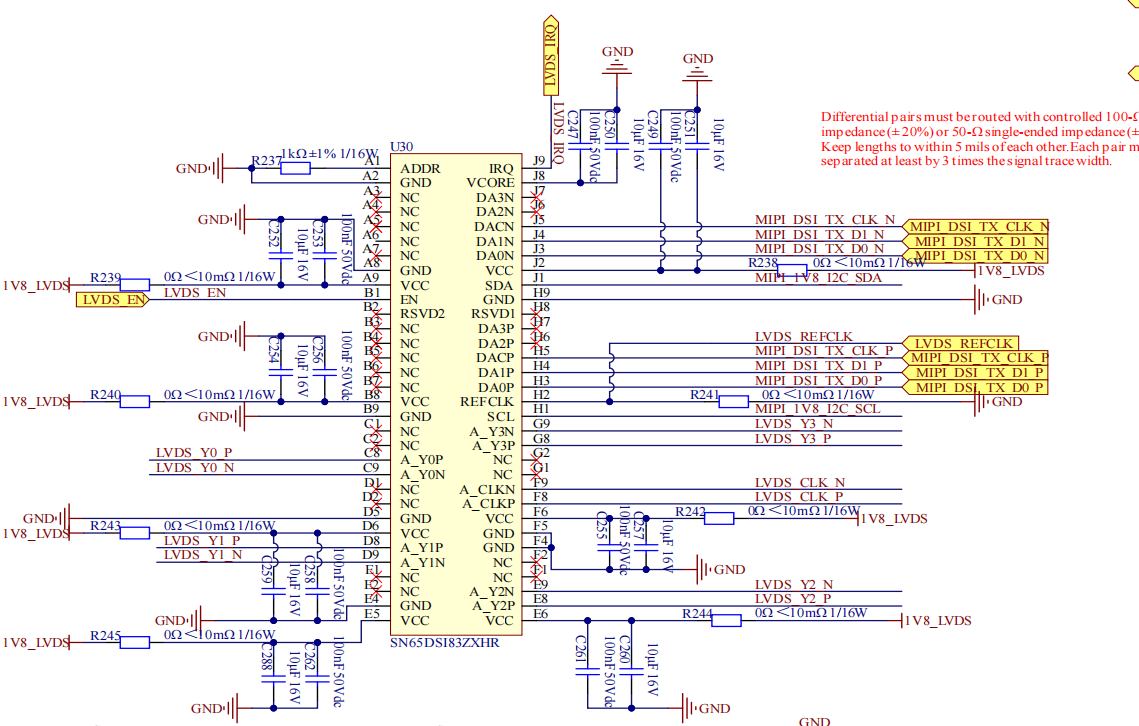

Part Number: SN65DSI83

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN65DSI83

Hi Hailei,

For the EN pin, please check the datasheet initialization sequence the EN pin control. It describes when the EN pin should be set.

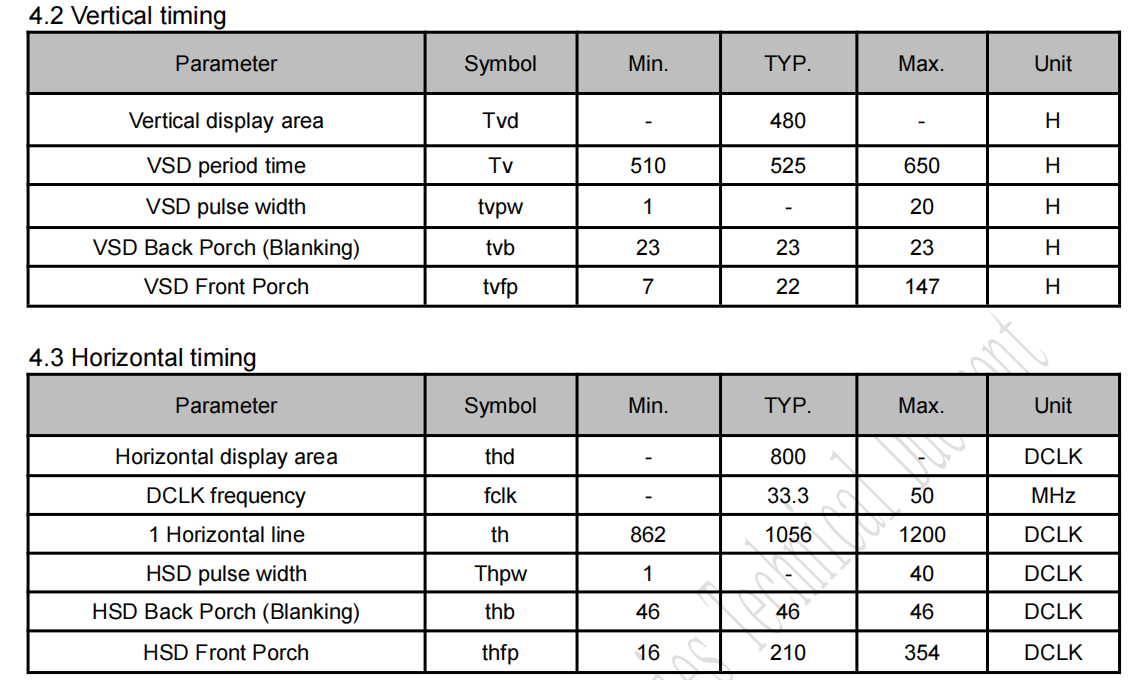

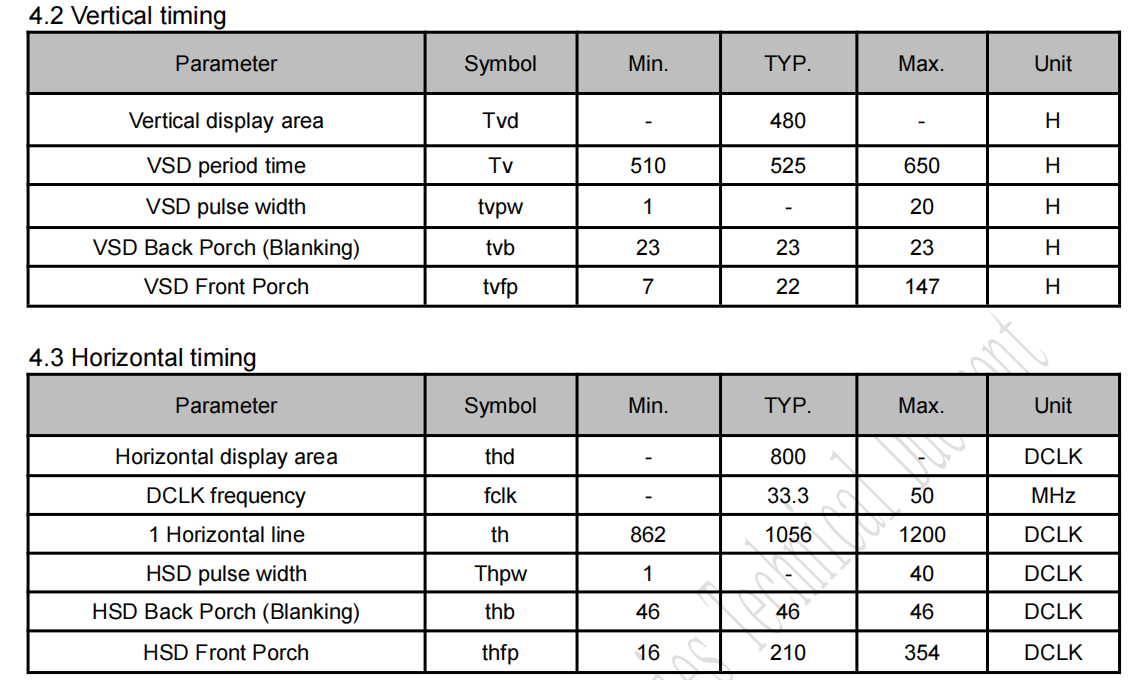

For using the REFCLK, there is an option in the DSI Tuner GUI to change clock source from DSI clock to REFCLK. And you can set the multiplier so that the LVDS clock output is a multiple of the REFCLK.

For example if the REFRCLK = 24 MHz, and the multiplier is set to 2, then the resulting output LVDS clock would be 48 MHz.

Best regards,

Ikram

Thanks,

Hi Hailei,

Our MIPI has 2 lanes, and the target LVDS for conversion needs to have 4 lanes. Is that okay?

Yes this should be okay. The LVDS output will be 3 or 4 lane, depending on the bits per pixel (color depth). And the input vary in number of DSI lanes used.

However, note that the device will have to be programmed based on number of DSI lanes used, and resulting DSI clock rate for that resolution.

Please let us know if you have further questions, or any queries about using the DSI Tuner tool.

Best regards,

Ikram

Hello,

The team is out due to a public Holiday in the US. Responses will be delayed until Monday.

Thank you for your patience

Hi Hailei,

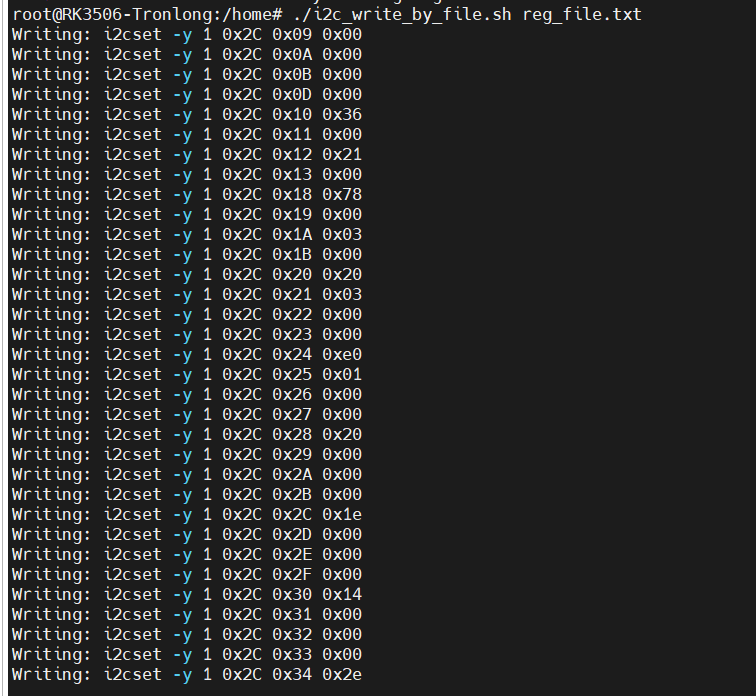

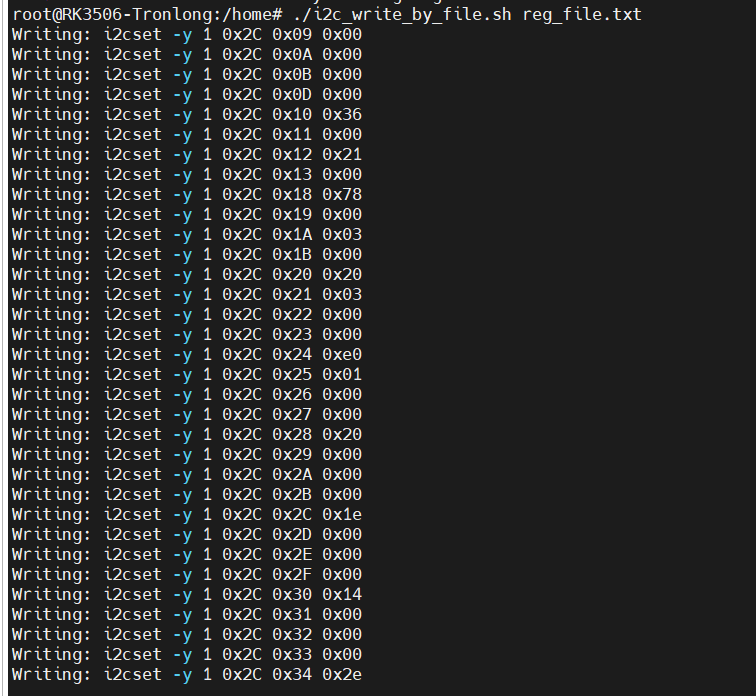

The data sheet seems to be inconsistent. The tool requires writing 0x36 to register 0x10, but bits 1 and 2 are not described in the data sheet.

These bits are ignored here since they are only used for channel B, which is not applicable here. This should be okay.

Did you try using the test pattern? Please program with test pattern enabled and check if the timings are okay.

It's possible that the REFCLK frequency and the DSI video data lanes do not match frequency exact causing this issue. What DSI clock frequency is the DSI source set to? Is it for precisely 32 MHz LVDS clock output as well?

Best regards,

Ikram