Part Number: DS90UB947-Q1EVM

Other Parts Discussed in Thread: DS90UB947-Q1, DS90UB948-Q1, ALP

Hello! When verifying our self-designed DS90UB947-Q1/DS90UB948-Q1 PCBA, the screen flickers continuously.

However, color display is normal. The touch panel on the LCM and the LP-8866-Q1 backlight brightness I2C control via FPD-link are functioning normally.

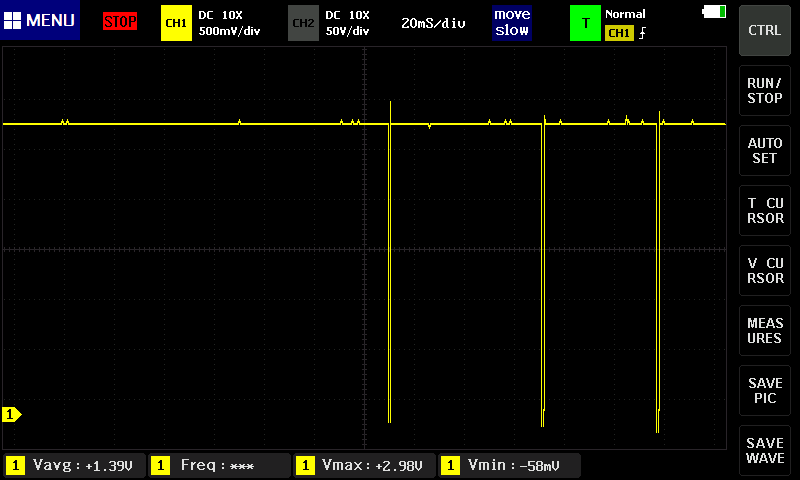

I2S is not used in this application. The LCD resolution is 1920x720, and the FPD-link cable length is 2 meters. Improving the power supply did not significantly improve the situation. The LOCK LED indicator on the DS90UB948-Q1 exhibits intermittent fluctuations.

The functionality was verified on an EVB before implementing the PCBA.

It is worth noting that the flickering problem was resolved after replacing the DS90UB947-Q1 or DS90UB948-Q1 with an EVB.

Therefore, we believe the problem lies in the FPD-link signal quality. However, our company lacks high-speed equipment for measuring FPD-link waveforms.

Even if we can measure the problem, we can't pinpoint its exact location.

Comparing the EVB signal to the temporary registers in our self-designed PCBA… we found no significant difference.

Therefore, I would like to ask which part of the temporary registers can be modified, or how to modify external components.

Attached is a video of LCM flickering and the lock signal waveform.