Part Number: TCA9801

Other Parts Discussed in Thread: TCA9803, TCA9802, PCA9517, TCA9517A, TCA9617B

Dear experts,

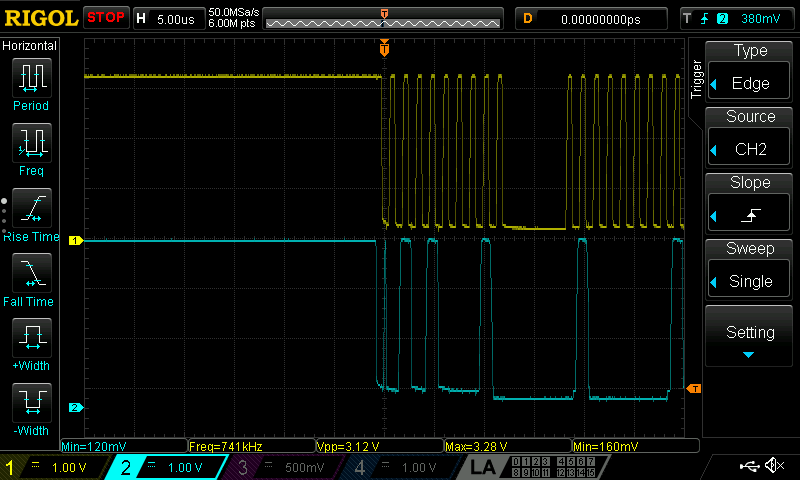

We're experiencing an issue where the logic low voltage of the first bit isn't low enough. This results in the PN7160 not being able to recover after reading invalid memory. The bus seems to remain operational, but operating out of spec for the PN7160.

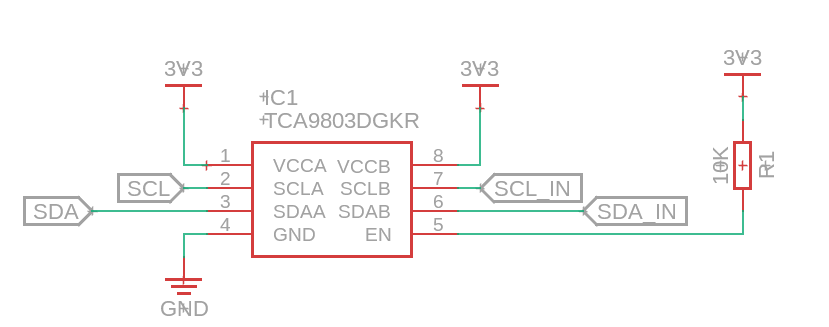

The measurements below are done at the B-side at the end of a 50cm ribbon-cable. There are 2K2 pull-ups on the A-side and none on the B-side. We've tested this with TCA9803, TCA9802 and TCA9801. Measurements below are with TCA9801.

Attached is also a capture performed with Logic 2 (Saleae). The out-of-bounds memory read happens at 10.509322 seconds.

Could you help us find a solution?

Best regards,

Jochem