Hi Ti,

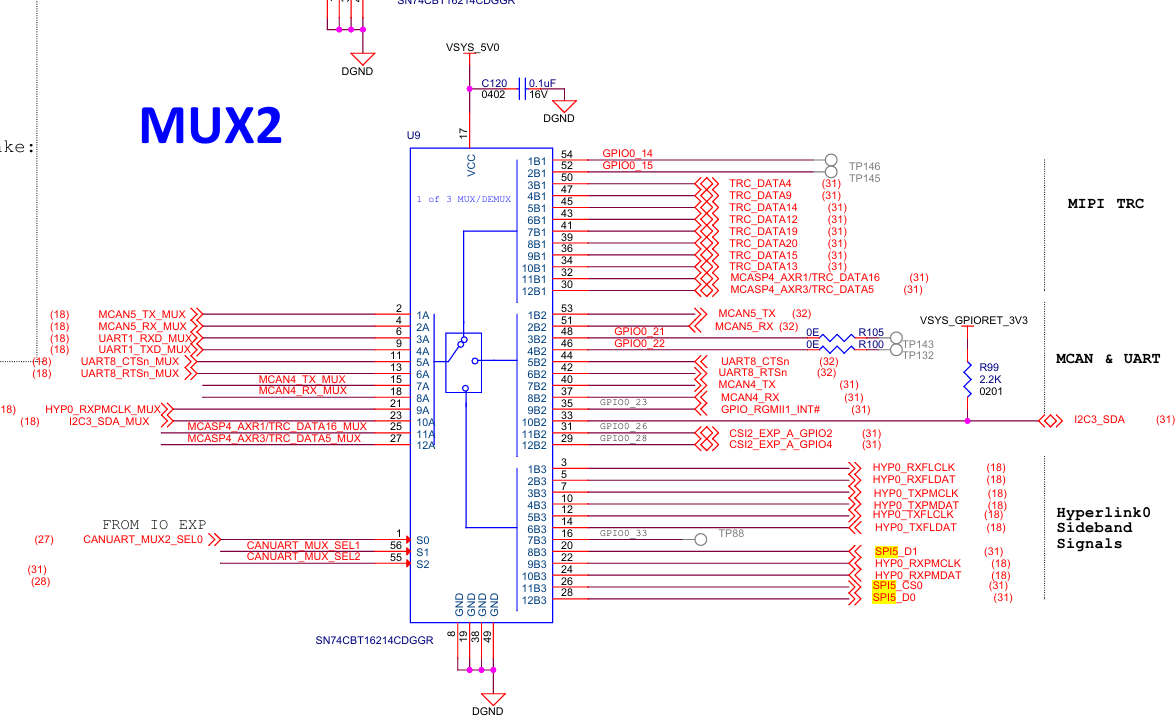

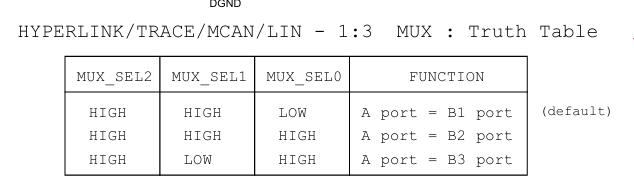

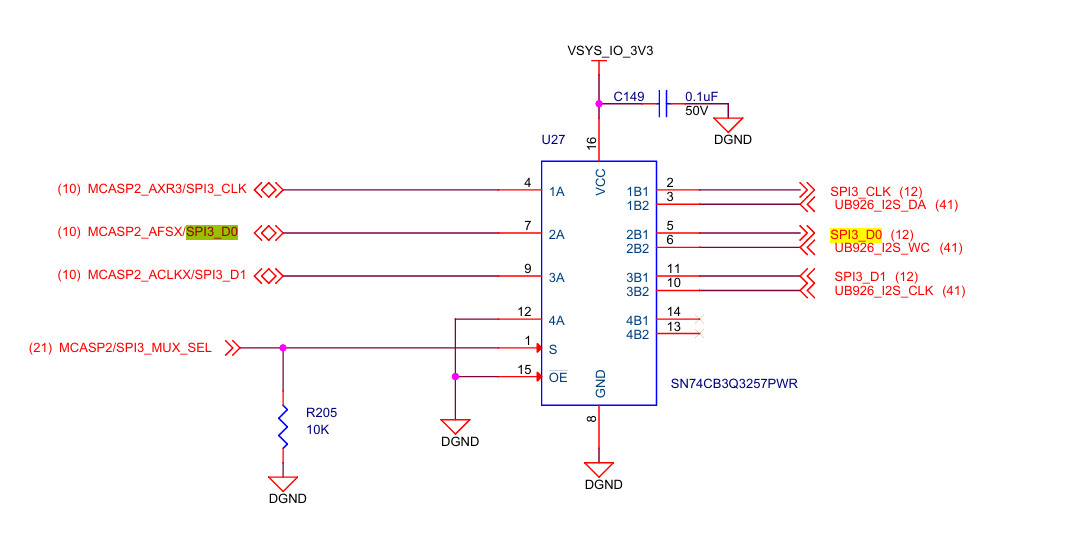

I want to test SPI external communication, so I'm using 'mcusw/mcal_drv/mcal/examples/Spi/mcspi_app/McspiApp.c' for testing. The circuit diagram shows that SPI5 needs to be used and 'CANUART_MUX' needs to be selected to port B3 for data transmission testing.

Therefore, I made the following modifications to 'McspiApp_Startup.c'.

mcusw/mcal_drv/mcal/examples/Spi/mcspi_app/soc/j721s2/mcu2_1/McspiApp_Startup.c: McspiApp_Startup.c

Currently, it seems that whether D0 and D1 are shorted or not, the log shows that 'rx' successfully received the data transmitted by 'tx'.

I believe that shorting D0 and D1 will make the UART log show that 'rx' successfully received the data from 'tx'; without shorting, the UART log will show a mismatch or an inability to receive data.

Is there anything wrong with my testing method, modification method, or idea?

Thanks a lot!!

Alice