Part Number: TUSB1004

Hello,

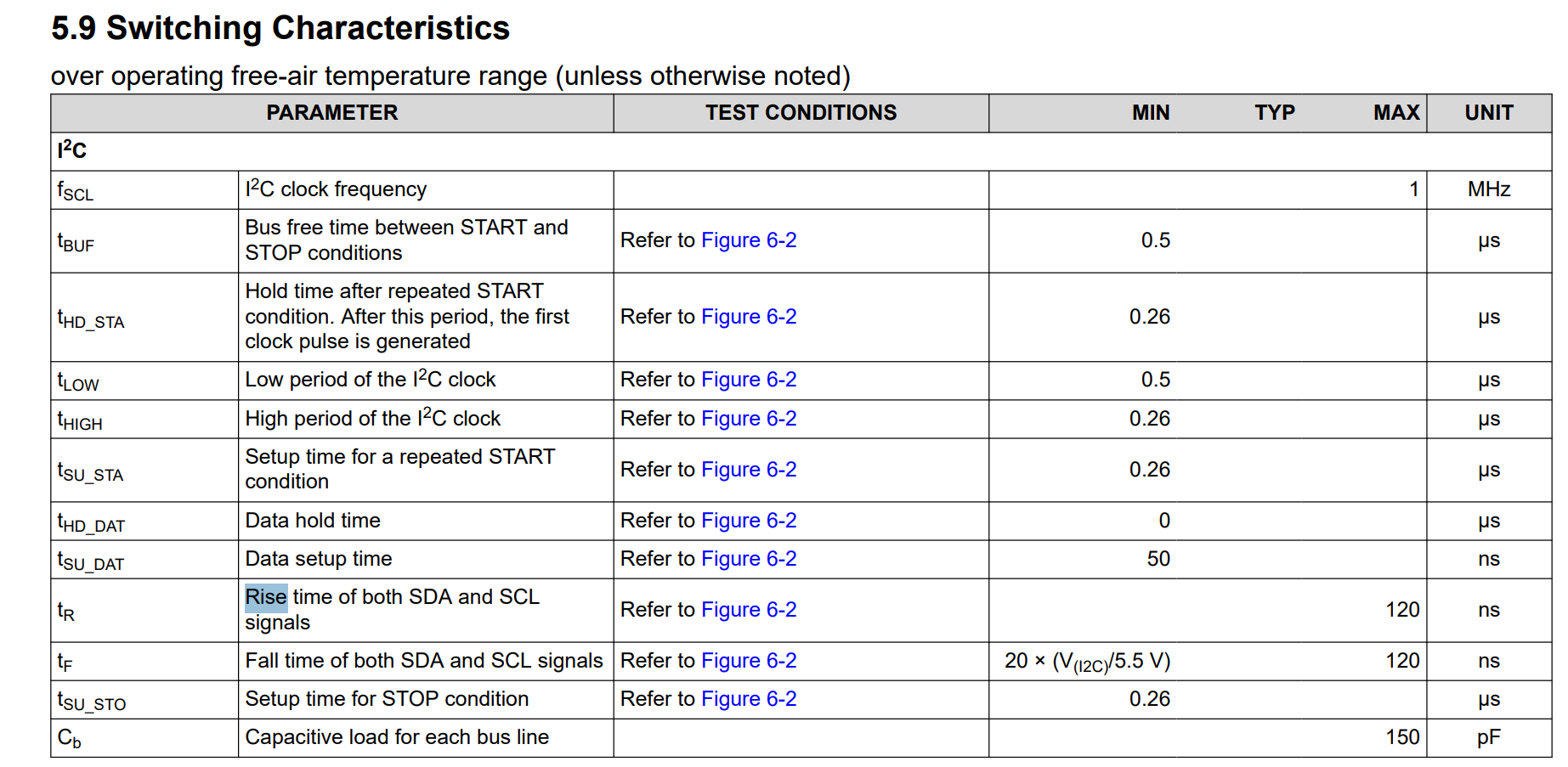

The TUSB1004 Datasheet indicates that the maximum rise time for the I2C SDA/SCL lines is 120ns maximum and the maximum Capacitive load for each line is 150pF while max clock rate is 1MHz (Fast-mode Plus I2C mode).

As you likely know, the I2C specification for standard mode is 100kHz max clock rate with 1000ns rise time and 400pF max bus capacitance while the specification for fast mode is 400kHz max clock rate with 300ns max rise time and 400pF max bus capacitance.

I would like to confirm that these 120ns and 150ps datasheet specifications apply only to I2C modes operating above 400kHz, and when operating below 400kHz, the part adheres to I2C standards (meaning at 400KHz or below, 300ns rise time with 400pF bus capacitance is acceptable while at 100KHz or below, 1000ns rise time with 400pF bus capacitance is acceptable).

I assume this is the case but would like to confirm.

Thanks!