Part Number: AM62P-Q1

Hi everybody,

I am working with the AM62P-Q1 processor, especially on the MDIO interface. I checked the processor MDIO and MDC timings and i found out that the Delay time, MDIO[x]_MDC low to MDIO[x]_MDIO valid timing was violated (the one in the image below, from component datasheet).

The processor software is currently using the TI driver to drive the MDIO interface.

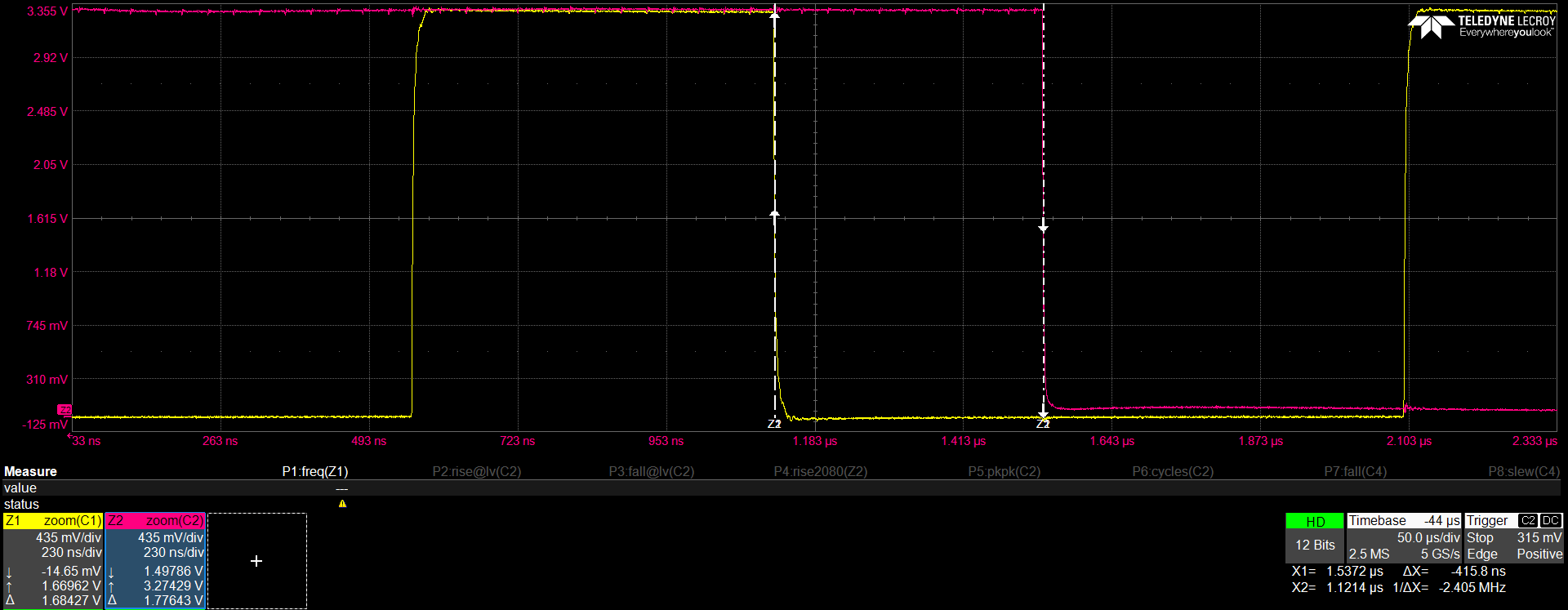

I share below the DSO snapshot about the timing violations (the yellow waveform is MDC and the red one is MDIO).

Do you have any suggestions to improve this timing situation? Thank you for the support.

Best regards,

Michele.