Other Parts Discussed in Thread: SN65LVDT41

HiTI

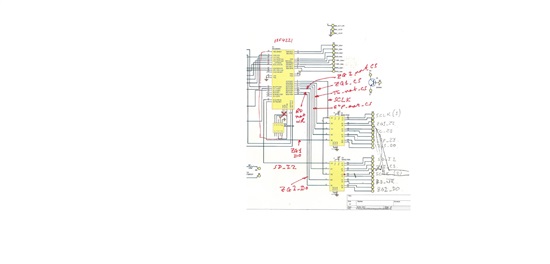

I am using a PIC 18F4221 to drive Serial clock into 2 SN65LVDT41's drivers.Are you allowed to drive 1 clock into 2 separate drivers? The clock output only comes through on one of the drivers,although both using the same clock.Do you need to drive the each driver from separate pin(clock) from the PIC or is one clock sufficient?

Regards Mitesh