Other Parts Discussed in Thread: DP83848C

Hi,

We are trying to build a sensor platform using the DP83848C physical layer ethernet interface. We took the SmartFusion Evaluation Kit from Microsemi (http://www.actel.com/products/hardware/devkits_boards/smartfusion_eval.aspx) as our reference design, and built our board basically copying the relevant parts from their schematic, the only difference being the RJ-45 connector. We've found that our boards fail at the autonegotiation step, no link is established.

Here is what we have tried so far:

1. We've made sure that supply voltage and 50 MHz clock are present, device is not powered down (pin 7), and is not reseting (pin 29).

2. With autonegotiation and Auto-MDIX turned on we've measured the signals on both the TD and RD pins, and verified that normal link pulses (NLP as defined in the autonegotiation specification) are present. We've found however that the signals look unlike the ones seen in Application Note 1519 DP83848.

3. If connected to an ethernet hub our device was not able to successfully autonegotiate, even though the ethernet hub was sending fast link pulse bursts with the acknowledge bit on, meaning that it had correctly received the link code word from our device.

4. We've assumed that the inability of our device detecting link code words from the hub, and the difference in pulse shapes are due to the different RJ-45 connector (J0G-0007NL as opposed to . Unfortunately they were not pin compatible, so we've used a 2 inch long ribbon cable to connect to the PCB.

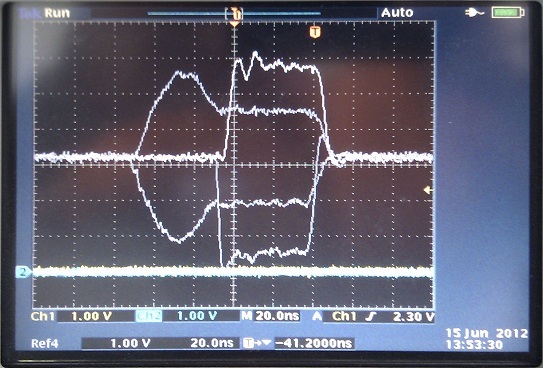

The pulse shapes were still different, our device was still unable to detect link code words. In the picture the longer signals are the differential signals measured on the working evaluation kit, the shorter signals with the higher amplitudes are the differential signals we have measured on our board.

5. We've checked our software as well, we start out with a reset (bit 15 in BMCR), then we wait more than 3 us and enable autonegotiation (bit 12), restart autonegotiation (bit 9), and enable collision test (bit 7) with one write to BMCR.

Any ideas what else we could/should check?

Our design is open-source ( http://code.google.com/p/marmote/source/browse/#svn%2Ftrunk ) the schematics of the board can be found here: http://code.google.com/p/marmote/source/browse/trunk/hardware/MainBoard_RevA/MainBoard_RevA_Sch.pdf (click "View raw file" to download pdf).

Thanks,

Benjamin