Other Parts Discussed in Thread: TSB83AA23

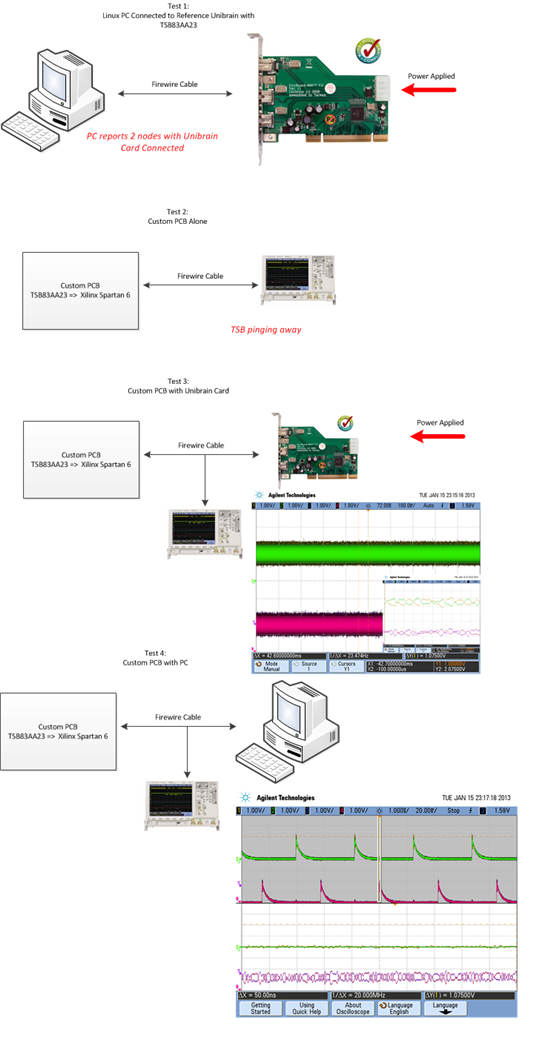

I've got a design using a TSB83AA23. I've noted the other conversations with regards to achieving sync between two 1394b nodes (attempting a 400b interface here).

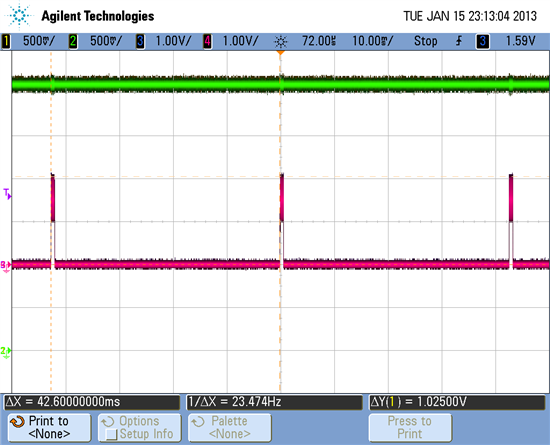

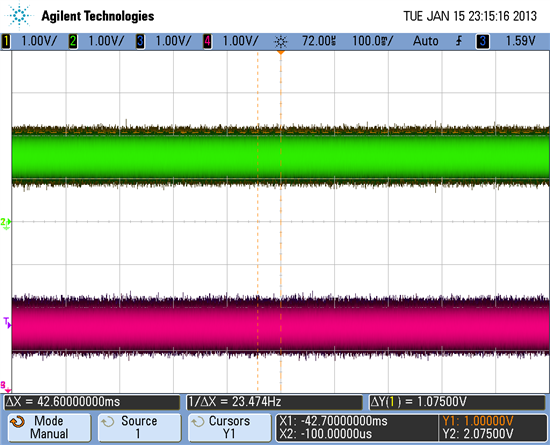

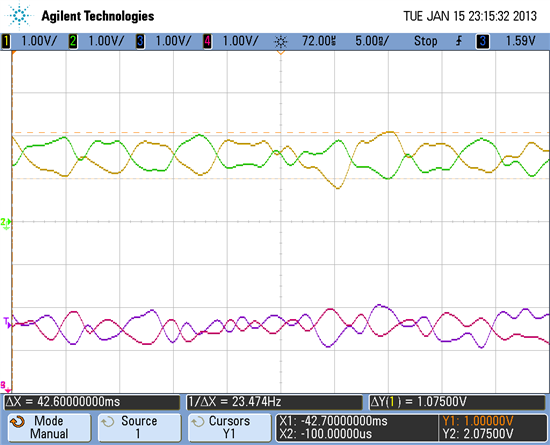

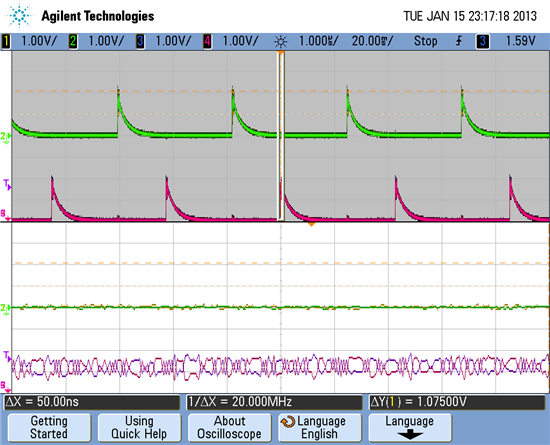

I can confirm that the TPA and TPB are toning but not achieving sync. I suspect that BMODE and CPS are incorrectly connected. I've attached the schematics. Can someone comment on those connections and see if they can spot any others I should consider.