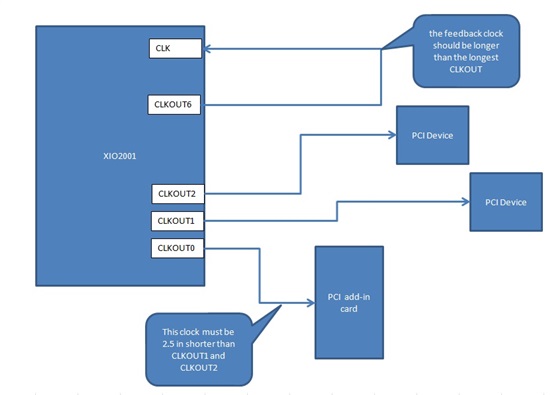

In the XIO2001 datasheet (SCPS212F Rev May 2012) it says to route the PCI clock being fed back to the XIO2001 (CLKOUT6 to CLK) 2.5 inches longer than the other device clocks (which probably delays it about 0.3 nsec) – which is a lot of extra routing. We have one PCI device (in an FPGA) that is only about 0.25 inches away and I’m worried about skewing the clocks this much. So, if we do not include this additional 2.5 inches (approx. 0.3 nsec) of clock skew can we simply offset the timings in Section 7.9 (which may not meet the PCI standards but as long as we can meet the new timings in our FPGA it shouldn’t matter)?