Other Parts Discussed in Thread: SN65HVD33

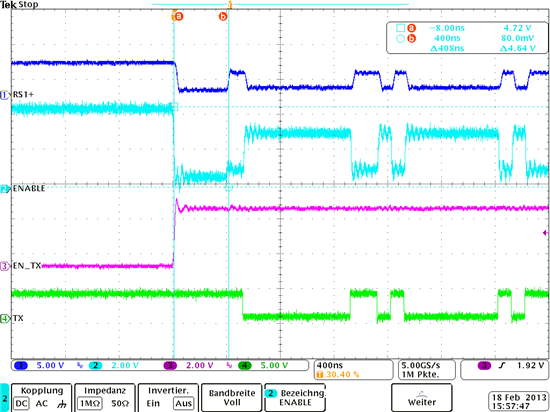

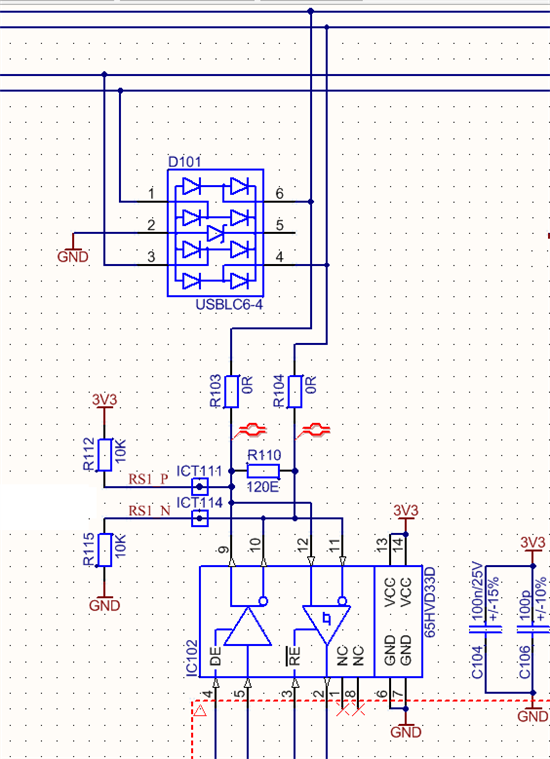

during verification of our design, we’ve found out, that the transmission ready time for SN65HVD33 is bus termination dependent. If the bus is terminated by two 120R resistors on each end, the input state is several ns later on the RS output. If our bus is additional biased with an 10k resistor to vcc and another 10k to gnd, the output stage needs more than 400ns to be ready.

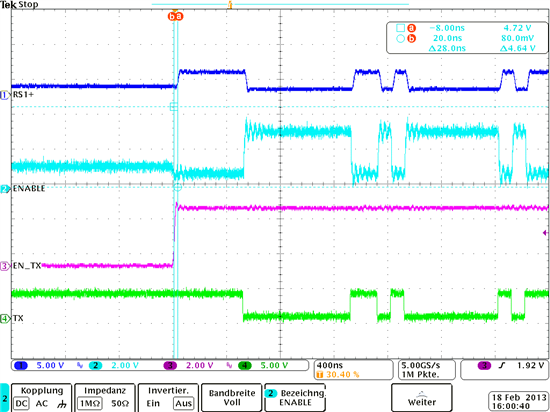

2x120R

2x120R and 2x10k (to vcc/gnd)

Hint: Channel 2 description is wrong, the measure shows RS- line.

does anyone have an explanation for this behavior?

BR