Hi,

I am currently evaluating the SERDESUB-21USB kit and I am experiencing problems with the I2C interface when operating the SERDES chip set in the Display mode, and I was hoping somebody could point me in the right direction as to what might be causing me the problem.

The SERDESUB-21USB link is working reliably (Lock signal stable, witnessed by setting a trigger for falling edge) and I am providing a 20 MHz signal on the Ser (PCLK pin), for which I am recovering reliably at the Des end (PCLK pin). Also the GPIO pin(s) functionality is working correctly; therefore I am confident that the SERDES link is working reliably.

A Diagram of my I2C set-up is shown as follows:-

With reference to the SERDESUB-21USB (P21) User’s Guide the Dill switches for configuring Master / Slave relationship (M_S pin) have been set as follows:-

- DS90UB903Q = H (Slave)

- DS90UB904Q = L (Master)

I2C bus speed at the Master is configured as 100 kHz

Also in line with configuring the set-up the following register values have been set:-

SER 0x06 = 0xC0 (Default anyway at power-up)

SER 0x07 = 0x9A

DES 0x08 - 0x17 = 0x00 (Default)

The problem I am experiencing is when trying to send a command to the AR1021 (Touch screen controller), which have been verified as working correctly when not passing the I2C over the SerDes link.

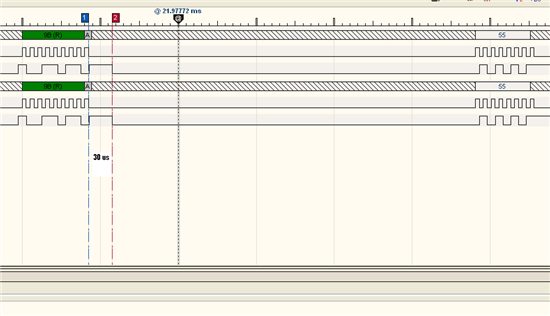

An example command (Bytes seen) has been provided within the attached file (Image insertion proivded poor quality) see screen shot of the logic analyser image highlighting the issue I am seeing. Logic Analyser connections are made at I2C_SER at the O/P of the Microchip Serial Analyser and I2C_DES at the O/P of the DS90UB904Q Deserialiser.

Disable Touch

Send: - 0x9A, 0x00, 0x55, 0x01, 0x13 This is sent O.K and timing seems O.K (Approx 1us delay between SER and DES clock pulses)

Receive: - 0x9B, 0x55, 0x02, 0x00, 0x13 Clock pulses are seen on the Des line, when 0x55 is sent by the AR1021 however these are not being re-produced on the Ser I2C bus and timing appears to become sparadic ?

From looking at the datasheet and also from correspondance from Microchip both the Master (Serial Analyser) and Slave (AR1021) both support clock stretching....

Any ideas on resolving this issue would be appreciated as I am keen to implement this chip set in my future design.

Thanks Lee Smith