Other Parts Discussed in Thread: DS92LX1621

I am attempting to get an Aptina MT9M131 CMOS image sensor connected up to an OMAP L138 processor via a SerDes link DS92LX1621/1622.

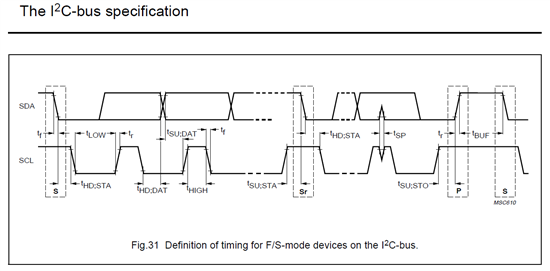

The SerDes link is solid and not having any synchronization or lock issues. My problem occurs while trying to configure the image sensor across the SerDes I2C link. There are 2 timing issues that I have noticed. First is that the MT9M131 "2-wire serial interface" is not claiming to be I2C compliant. And it is not: a 600ns hold time on SDA is required following falling edge of SCL. The official I2C standard only states that SDA must change while SCL is low - there are no setup or hold times required. The ideal transition places the SDA change in the middle of the low SCL period. The second timing issue is with the '1621 master proxy function. The '1621 is changing SDA simultaneously with the falling edge of SCL, not after the falling edge of SCL, as the I2C standard requires.

Either of these timing violations could cause a compatibility problem, but the two together make for an even worse situation. As far as I can tell, I have no control to change any of this. Although the OMAP side of the bus would correctly communicate with the image sensor, the "repeated" side of the I2C cannot.

Any work-around's that I can do? I'm going to try to delay SDA using a capacitor, but I certainly can't get a 600ns delay. I suspect much less is actually needed, since I have observed an occasional "ACK" from the part, even with the timing as it is.

I would expect many people to have issues using the I2C functionality of this SerDes pair, since it doesn't really follow the I2C standard.

I have attached several scope traces showing the issues. There are 2 I2C busses shown: channels 3&4 are at the OMAP, and channels 1&2 are the repeated bus between the Ser and the image sensor.

Channels 3&4 show the idealized I2C SDA transition point.

When repeated by the Ser, it can be seen that SDA change is simultaneous with falling edge of SCL.

Thanks in advance for any help or suggestions.

David