I am trying to TFTP boot a Linux kernel on a Freescale MPC8313e-rdb PowerPC. The bootloader is u-boot 2012.04 where I've added the DP83640 phy driver and the ethloop test case.

The TFTP server is a Ubuntu 10.04 machine with xinetd tftp service.

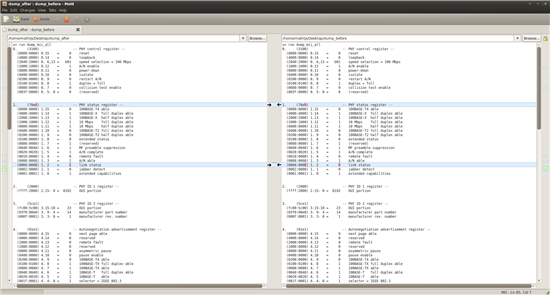

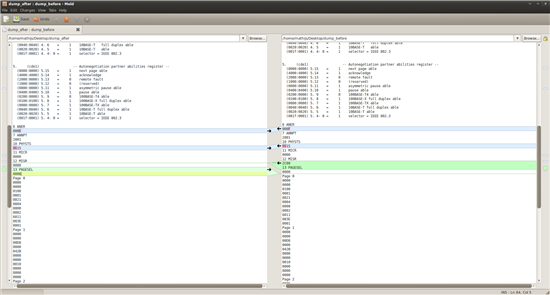

When I try to load a file (e.g. Linux kernel) through tftp the phy incedentially generate errors (approximately at 1 % of the cases). The tsec driver tells me that I got a CRC and/or a NONOCTET error (0x0004 and 0x0010 resp.) I haven't configured any register, the only thing I've done is reset the PHY by writing 0x8000 in the BMCR.

I've tried a 100mbit full duplex, half duplex and a 10 mbit half duplex connection, but all speeds fail in 1 % of the packets. On normal conditions, there are 562 bytes captured by the MAC, but when the faulty packets are received, sometimes 563 or 564 bytes are read.

When I memory dump the received packets, and compare them with the send packets something strange shows. Please keep in mind that in the memory dump of the received packets, I print 16 extra bytes, just to show any gibberish when available.

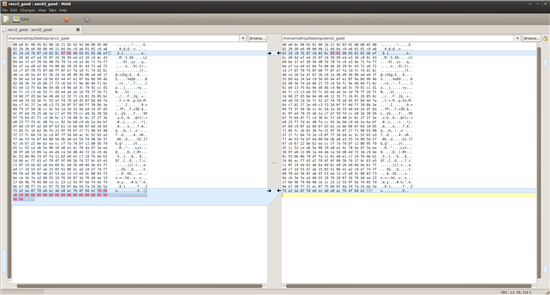

A good packet looks like this (received on the left, send on the right)

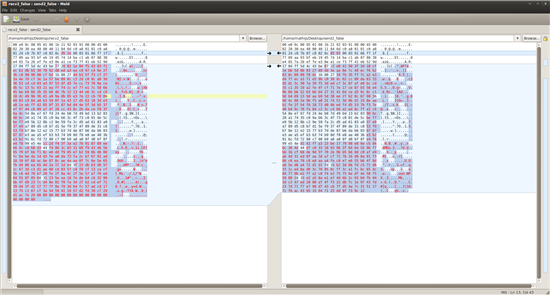

A faulty packet looks like this (received on the left, send on the right)

To determine where the problem may lay, I've enabled the loopback (0x7100 in BMCR) and wrote 1024 bytes to the phy and then read back the data to compare each packet. I've run this test 10.000 times, no errors are generated. Then I've disabled the loopback and inserted an ethernet RJ45 loopback adapter and rerun the tests. No errors are generated. I'm flabbergasted...

What could be the (possible) problem here?

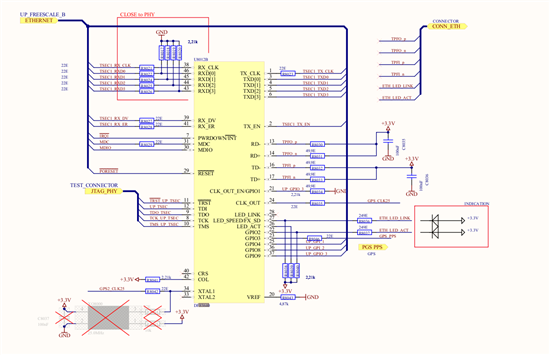

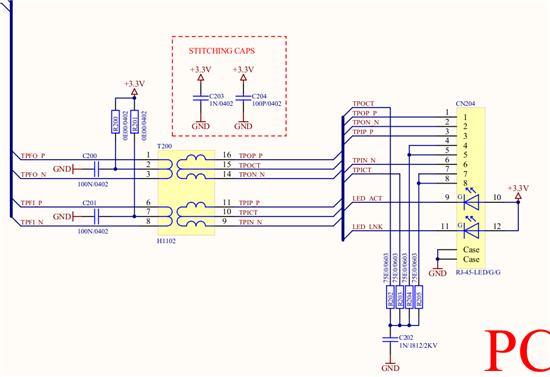

My ethernet chain consists of the following components:

- Freescale MPC8313E-RDB PowerPC

- TI DP83640 PHY

- Pulse Engineering H1102 10/100BASE-T Magnetics

Many thanks in advance and when you need more information, please let me know!

Mathijs