I'm trying to understand the speed at which the driver is enabled in the case where the DE and RE# lines are tied together. So in particular let's assume the following sequence of events:

- Sitting in "steady state" where DE = RE# = 0, i.e. receiver on, driver off.

- Transition to DE = RE# = 1, i.e. receiver off, driver on.

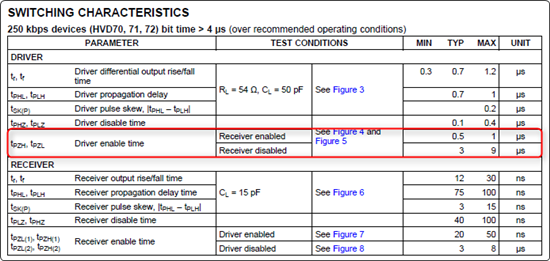

I look at the data manual and see the following:

The spec I've circled seems to assume the receiver is either enabled or disabled. Now one interpretation might be that this is referring to the initial condition, and so in my case my "steady state" has the receiver enabled. Therefore I should expect a maximum driver enable time of 1us. On the other hand, since both signals are transitioning I need to be sure that I'm not going to see a delay of 9us. At 115.2 kbaud that would be an entire bit time!

For further background, this actually relates to my other thread I posted about "auto direction" transceivers. Another avenue I'm pursuing is to simply tie the TXD input of the transceiver to a fixed state, add pullups on the outputs, and use the UART's Tx signal (inverted) to drive the DE/RE# pins. In this scenario when I transmit data from the UART the DE/RE# pins will be toggling at the UART baud rate so I need to be sure the transitions seen on the RS-485 bus can keep up.