Hi all,

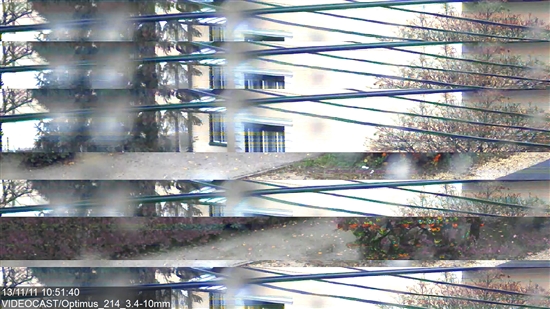

We use the Aptina's AR0331 3MP WDR image sensor with TI's SN65LVDS324 LVDS parallel converter in our DM814x based IP camera. It seems that if we pause the sensor streaming (which is frame synced and does not produce bad frame) the LVDS324 will go crazy and eliminate frame sync signals. This results broken pictures (see below). What's wrong? How could we fix it?

Regards,

Lajos