Other Parts Discussed in Thread: TUSB1310A

Hi, experts

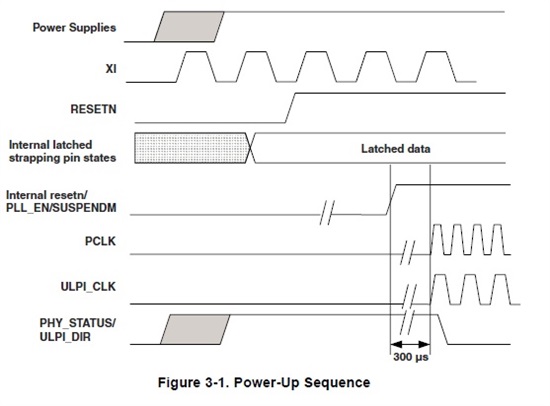

I designed a board based on TUSB1310A, while I can't generate PCLK.

I'm sure power rails are ready, there is nothing wrong with 40MHz clock input, and OUT_ENABLE is pulled up.

a) I'm confused about "Internal resetn/PLL_EN/SUSPENDM", is it a signal I should control, is it PHY_RESETN?

b) About PHY_STATUS/ULPI_DIR, should I control this pin, what do you mean by it in this diagram? I found PHY_STATUS/PIPE_16BIT was input/output pin, under which condition, it is input, or output?

c) The strap pins which are latched in my design are

XTAL_DIS/RX_ELECIDLE (1, clock input),

SSC_DIS/TX_MARGIN0 (1, SSC disabled),

PIPE_16BIT/PHY_STATUS (don't know how to deal with),

ISO_START/ULPI_DATA7 (0, not isolate),

ULPI_8BIT/ULPI_DATA6 (0),

REFCLKSEL1/ULPI_DATA5 (1),

REFCLKSEL0/ULPI_DATA4 (1)

Is there anything I missed?

Thanks.

Chris.