Other Parts Discussed in Thread: TLK10022, TLK10002

Dear....

I'd like to ask about clock recovery in Rx-Flow again.

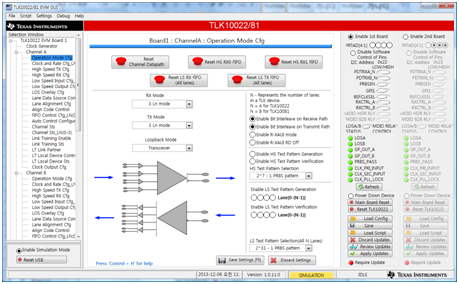

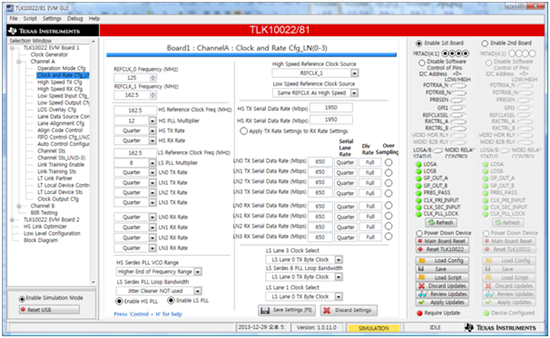

11. Mode = 3:1

22. Let's assume low side line rate = 65Mhz * 10Bit

33. Then, high side line rate = 65Mhz * 10 * 3

44. High side recovered clock, HS_RXBCLK_A/B = 65Mhz * 10 * 3 /20

(Page 20, 5.2 is saying that 1. HS_RXBCLK_A/B: recovered byte clock synchronous with incoming serial data and with a frequency matching the incoming line rate divided by 20.)

55. This 20-divided clock can be devided 1,2,4,5,8,....by register setting.

Q1 : How can I get 65Mhz (without dividing factor 3) ??

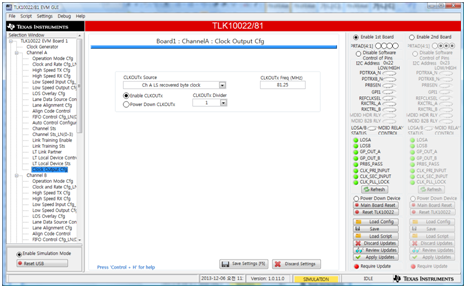

66. On page, Table 6-30

Bit[3:0] : CLKOUT_SEL[3:0] == 0110 = Selects Ch A LS recovered byte clock as output clock

Q2 : Selection of LS recovered clock (0110) may be the solution, I think.

However, the data sheet does not give a clear explanation.

Could you tell me the details about this?

Best Regards,

K.I. Koo