Other Parts Discussed in Thread: TUSB1310A

Hi,

I have a development board that installed a TUSB1310A.

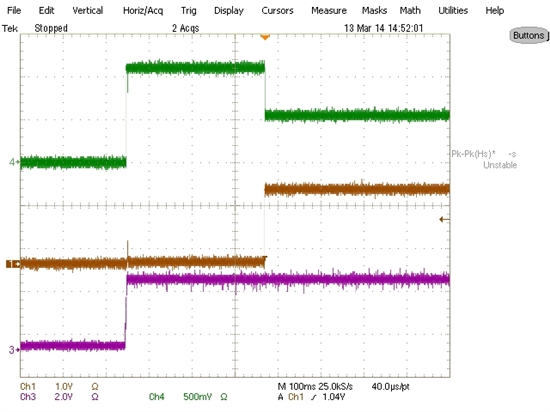

I notice one board has a common mode voltage of 500mV on TX DP and DM pins.

Even though I force a reset to this phy chip, the common mode output remains .

What can cause this symptons?