Other Parts Discussed in Thread: CDCM7005, TLK10002

Hi,

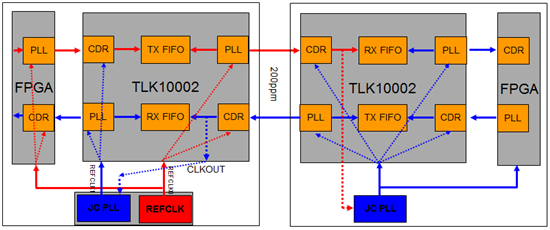

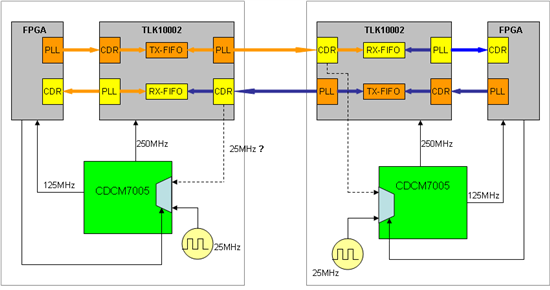

Here is my system setting,

1) TLK10002 works at 4:1 mode, HS speed is 10Gbps, LS side is 2.5Gbps, the reference clock is 250MHz generated by a CDCM7005 PLL

2) LS side is connected to 4 transceivers in an Altera Cyclone IV GX FPGA

3) Both transmission terminals have the same settings. They are connected by a 10Gbps optical fiber link.

After system being booted up,both terminals show lane alignment OK. And LOS signals are low. Now, i transmit a fixed pattern data from one terminal, let's say terminal A. So called fixed data means at lane 0 a 9'h1BC (K28.5) byte at lest significant byte is always transmitted. At the other terminal, let's say terminal B, the data received by transceivers in the FPGA is unstable, which means 1BC is not on lane 0 bit[7:0] or any fixed position unchanged but it jumps randomly in any position among four lanes. I don't know why. Is there anyone who can help me?

I've also checked the F register at terminal B to see the TLK10002 working status. I got the result of "5C2F". It doesn't look good. it says the RX FIFO underflow. What can cause it?

Looking forward to helps!