Hi all,

I have asked the same question on Linux forum as well:- http://e2e.ti.com/support/embedded/linux/f/354/p/354901/1246853.aspx#1246853.

I am posting it here, because i see questions about TLK110 more on Ethernet Forum than On Linux. Let me know if it is redundant.

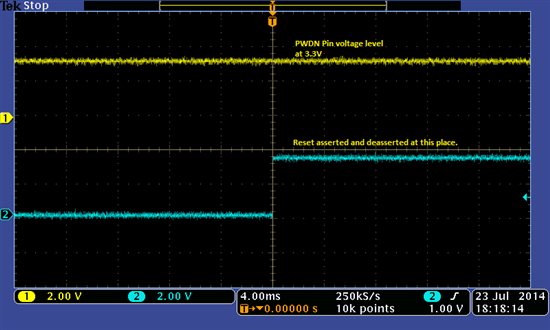

The issue is i am able to access MDIO registers through MDIO bus but RMII interface is not working, using oscilloscope i found out that even TX_EN pin is not high which should be high to enable transmission.

Kindly help.

Thanks and Regards,

Prateek