Dear Team:

Our customer used SN65DSI86 in their panel, but some panels are work, the others are failed that panel are all black screen. The work panel which we measured I2C and DSI clk gotten key point siganl is as below,after loaded initial command file. The fail panelscould not get key point signalas same rpocedureand down DSI86 register got CHA_SOT_SYNC_ERR.

Do you have any idea about this?

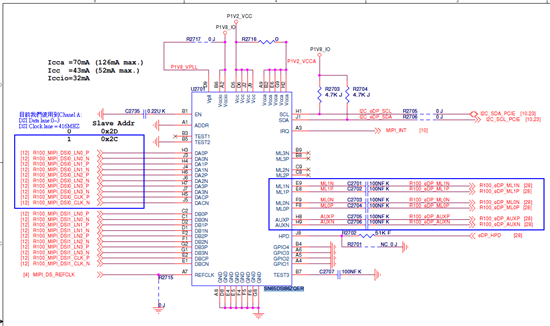

The circuit and register setting are as below.

When load command initial file,

void sn65dsi86_dsi2edp_enable_early(void)

{

struct sn65dsi86_platform_data *dsi2edp = sn65dsi86_dsi2edp_pdata;

int pmic_gpio5 = PM8921_GPIO_PM_TO_SYS(5); //open 1P2& 1P8 power for SN65DSI86

if (dsi2edp && dsi2edp->dsi2edp_enabled)

return;

printk("sn65dsi86_dsi2edp_enable_early\n");

mutex_lock(&dsi2edp->lock);

usleep_range(100,200);

gpio_set_value_cansleep(pmic_gpio5, 1);

mdelay(100);

sn65dsi86_reg_write(dsi2edp,SN65DSI86_SOFT_RESET,0x01);

usleep_range(10000, 12000);

//disable VSTREAM

sn65dsi86_reg_write(dsi2edp, SN65DSI86_FRAMING_CFG, 0x00);

//usleep_range(10000, 12000);

/* PLL ENABLE */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_PLL_EN, 0x00);

//usleep_range(10000, 12000);

/* reset */

//sn65dsi86_reg_write(dsi2edp,SN65DSI86_SOFT_RESET,0x01);

//usleep_range(10000, 12000);

/* STEP3: Single channelA 4 DSI lanes */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_DSI_CFG1, 0x26);

//usleep_range(10000, 12000);

/* STEP4: set external REFCLK 19.2MHz */

//sn65dsi86_reg_write(dsi2edp, SN65DSI86_PLL_REFCLK_CFG, 0x02);//Alex_Fang_test

//usleep_range(10000, 12000);

/* STEP4: set DPLL REFCLK 416MHz */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_PLL_REFCLK_CFG, 0x04);

usleep_range(10000, 12000);

/* DSI CLK FREQ 415MHz */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_DSI_CHA_CLK_RANGE, 0x52);

//usleep_range(10000, 12000);

/* STEP8: HPD ENABLE */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_DP_HPD_EN, 0x01);//disable HPD

//usleep_range(10000, 12000);

/* STEP9,10,11: eDP Pannel DisplayPort configuration(DPCD) */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_DP_SSC_CFG, 0x24); /* Pre0dB 2 lanes no SSC */

//usleep_range(10000, 12000);

sn65dsi86_reg_write(dsi2edp, SN65DSI86_DP_CFG, 0x80);/* DP_DATARATE HBR 2.70Gbps per lane */

//usleep_range(10000, 12000);

/* CHA_ACTIVE_LINE_LENGTH */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_VIDEO_CHA_LINE_LOW, 0x80);

//usleep_range(10000, 12000);

sn65dsi86_reg_write(dsi2edp, SN65DSI86_VIDEO_CHA_LINE_HIGH, 0x07);

//usleep_range(10000, 12000);

/* CHA_VERTICAL_DISPLAY_SIZE */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_CHA_VERT_DISP_SIZE_LOW, 0x38);

//usleep_range(10000, 12000);

sn65dsi86_reg_write(dsi2edp, SN65DSI86_CHA_VERT_DISP_SIZE_HIGH, 0x04);

//usleep_range(10000, 12000);

/* CHA_HSYNC_PULSE_WIDTH */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_CHA_HSYNC_PULSE_WIDTH_LOW, 0x24);

//usleep_range(10000, 12000);

sn65dsi86_reg_write(dsi2edp, SN65DSI86_CHA_HSYNC_PULSE_WIDTH_HIGH,0x80);

//usleep_range(10000, 12000);

/* CHA_VSYNC_PULSE_WIDTH */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_CHA_VSYNC_PULSE_WIDTH_LOW, 0x05);

//usleep_range(10000, 12000);

sn65dsi86_reg_write(dsi2edp, SN65DSI86_CHA_VSYNC_PULSE_WIDTH_HIGH,0x80);

//usleep_range(10000, 12000);

/* CHA_HORIZONTAL_BACK_PORCH */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_CHA_HORIZONTAL_BACK_PORCH, 0x64);

//usleep_range(10000, 12000);

/* CHA_VERTICAL_BACK_PORCH */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_CHA_VERTICAL_BACK_PORCH, 0x0C);

//usleep_range(10000, 12000);

/* CHA_HORIZONTAL_FRONT_PORCH */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_CHA_HORIZONTAL_FRONT_PORCH, 0x20);

//usleep_range(10000, 12000);

/* CHA_VERTICAL_FRONT_PORCH */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_CHA_VERTICAL_FRONT_PORCH, 0x05);

//usleep_range(10000, 12000);

/* RIGHT_CROP */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_RIGHT_CROP, 0x00);

//usleep_range(10000, 12000);

/* LEFT_CROP */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_LEFT_CROP, 0x00);

//usleep_range(10000, 12000);

/* DP-18BPP Enable */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_DP_18BPP_EN, 0x01);

//usleep_range(10000, 12000);

sn65dsi86_reg_write(dsi2edp, SN65DSI86_DSI_CFG2, 0x00);

usleep_range(100, 200); //Alex_Fang_PowerSeq

//usleep_range(10000, 12000);

}

下半部initial command:

void sn65dsi86_dsi2edp_enable_lately(void)

{

struct sn65dsi86_platform_data *dsi2edp = sn65dsi86_dsi2edp_pdata;

unsigned short int buff;

unsigned int val = 0;

if (dsi2edp && dsi2edp->dsi2edp_enabled)

return; //Alex_Fag_test

printk("sn65dsi86_dsi2edp_enable_lately\n");

/* PLL ENABLE */

//usleep_range(300, 400);

sn65dsi86_reg_write(dsi2edp, SN65DSI86_PLL_EN, 0x01);

/* STEP12: check DP_PLL_LOCK */

do{

val = 0;

sn65dsi86_reg_read(dsi2edp, SN65DSI86_PLL_REFCLK_CFG, &val);

if((val & 0x80) != 0)

{

printk("sn65dsi86_dsi2edp_enable DP_PLL_LOCK=%x(LOCK)\n",val);

}

else{

printk("sn65dsi86_dsi2edp_enable DP_PLL_LOCK=%x(UNLOCK)\n",val);

}

}while((val & 0x80) == 0);

/* STEP13: use Native AUX interface to enable eDP panel ASSR */

buff = EDP_EN_ASSR;

sn65dsi86_dsi2edp_write_dpcd(&buff,EDP_CONFIGURATION_SET_ADD,1);

//usleep_range(10000, 12000);

msleep(75); //Alex_Fang_PowerSeq

/* STEP14: DisplayPort Link Semi-Auto train */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_ML_TX_MODE, 0x0a);

usleep_range(10000, 12000);

val =0;

sn65dsi86_reg_read(dsi2edp, SN65DSI86_ML_TX_MODE, &val);

if((val & 0x0F) == 0x1)

printk("DisplayPort Link Semi-Auto train Success!!\n");

else

printk("DisplayPort Link Semi-Auto train Fail(%x)!!\n",val);

//use Native AUX interface to check display panel DPCD information

if(0)

sn65dsi86_dsi2edp_showDPCDInfo();

sn65dsi86_reg_write(dsi2edp, SN65DSI86_ML_TX_MODE, 0x01);//set to normal mode

usleep_range(10000, 12000);

/* COLOR BAR */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_COLOR_BAR_CFG, 0x08);//test pattern

usleep_range(10000, 12000);

sn65dsi86_reg_write(dsi2edp,SN65DSI86_SOFT_RESET,0x01);

usleep_range(10000, 12000);

/* enhanced framing and Vstream enable */

sn65dsi86_reg_write(dsi2edp, SN65DSI86_FRAMING_CFG, 0x08);

dsi2edp->dsi2edp_enabled = true;

mutex_unlock(&dsi2edp->lock);

}

//Register definition----------------------------------------------------

#define SN65DSI86_DEVICE_ID 0x00

#define SN65DSI86_DEVICE_REV 0x08

#define SN65DSI86_SOFT_RESET 0X09

#define SN65DSI86_PLL_REFCLK_CFG 0x0A

#define SN65DSI86_PLL_EN 0x0D

#define SN65DSI86_DSI_CFG1 0x10

#define SN65DSI86_DSI_CFG2 0x11

#define SN65DSI86_DSI_CHA_CLK_RANGE 0x12

#define SN65DSI86_DSI_CHB_CLK_RANGE 0x13

#define SN65DSI86_VIDEO_CHA_LINE_LOW 0x20

#define SN65DSI86_VIDEO_CHA_LINE_HIGH 0x21

#define SN65DSI86_VIDEO_CHB_LINE_LOW 0x22

#define SN65DSI86_VIDEO_CHB_LINE_HIGH 0x23

#define SN65DSI86_CHA_VERT_DISP_SIZE_LOW 0x24

#define SN65DSI86_CHA_VERT_DISP_SIZE_HIGH 0x25

#define SN65DSI86_CHA_HSYNC_PULSE_WIDTH_LOW 0x2C

#define SN65DSI86_CHA_HSYNC_PULSE_WIDTH_HIGH 0x2D

#define SN65DSI86_CHA_VSYNC_PULSE_WIDTH_LOW 0x30

#define SN65DSI86_CHA_VSYNC_PULSE_WIDTH_HIGH 0x31

#define SN65DSI86_CHA_HORIZONTAL_BACK_PORCH 0x34

#define SN65DSI86_CHA_VERTICAL_BACK_PORCH 0x36

#define SN65DSI86_CHA_HORIZONTAL_FRONT_PORCH 0x38

#define SN65DSI86_CHA_VERTICAL_FRONT_PORCH 0x3a

#define SN65DSI86_COLOR_BAR_CFG 0x3c

#define SN65DSI86_RIGHT_CROP 0x3d

#define SN65DSI86_LEFT_CROP 0x3e

#define SN65DSI86_ADEN 0x3f

#define SN65DSI86_FRAMING_CFG 0x5a

#define SN65DSI86_DP_18BPP_EN 0x5b

#define SN65DSI86_DP_HPD_EN 0x5c

#define SN65DSI86_GPIO_CTRL_CFG 0x5f

#define SN65DSI86_AUX_WDATA0 0x64

#define SN65DSI86_AUX_WDATA1 0x65

#define SN65DSI86_AUX_WDATA2 0x66

#define SN65DSI86_AUX_WDATA3 0x67

#define SN65DSI86_AUX_WDATA4 0x68

#define SN65DSI86_AUX_WDATA5 0x69

#define SN65DSI86_AUX_WDATA6 0x6a

#define SN65DSI86_AUX_WDATA7 0x6b

#define SN65DSI86_AUX_WDATA8 0x6c

#define SN65DSI86_AUX_WDATA9 0x6d

#define SN65DSI86_AUX_WDATA10 0x6e

#define SN65DSI86_AUX_WDATA11 0x6f

#define SN65DSI86_AUX_WDATA12 0x70

#define SN65DSI86_AUX_WDATA13 0x71

#define SN65DSI86_AUX_WDATA14 0x72

#define SN65DSI86_AUX_WDATA15 0x73

#define SN65DSI86_AUX_ADDR_19_16 0x74

#define SN65DSI86_AUX_ADDR_15_8 0x75

#define SN65DSI86_AUX_ADDR_7_0 0x76

#define SN65DSI86_AUX_LENGTH 0x77

#define SN65DSI86_AUX_CMD_SEND 0x78

#define SN65DSI86_AUX_RDATA0 0x79

#define SN65DSI86_AUX_RDATA1 0x7A

#define SN65DSI86_AUX_RDATA2 0x7B

#define SN65DSI86_AUX_RDATA3 0x7C

#define SN65DSI86_AUX_RDATA4 0x7D

#define SN65DSI86_AUX_RDATA5 0x7E

#define SN65DSI86_AUX_RDATA6 0x7F

#define SN65DSI86_AUX_RDATA7 0x80

#define SN65DSI86_AUX_RDATA8 0x81

#define SN65DSI86_AUX_RDATA9 0x82

#define SN65DSI86_AUX_RDATA10 0x83

#define SN65DSI86_AUX_RDATA11 0x84

#define SN65DSI86_AUX_RDATA12 0x85

#define SN65DSI86_AUX_RDATA13 0x86

#define SN65DSI86_AUX_RDATA14 0x87

#define SN65DSI86_AUX_RDATA15 0x88

#define SN65DSI86_DP_SSC_CFG 0x93

#define SN65DSI86_DP_CFG 0x94

#define SN65DSI86_TRAINING_CFG 0x95

#define SN65DSI86_ML_TX_MODE 0x96

#define SN65DSI86_IRQ_EN 0xE0

#define SN65DSI86_IRQ_STATUS0 0xF0

#define SN65DSI86_IRQ_STATUS1 0xF1

#define SN65DSI86_IRQ_STATUS2 0xF2

#define SN65DSI86_IRQ_STATUS3 0xF3

#define SN65DSI86_IRQ_STATUS4 0xF4

#define SN65DSI86_IRQ_STATUS5 0xF5

#define SN65DSI86_IRQ_STATUS6 0xF6

#define SN65DSI86_IRQ_STATUS7 0xF7

#define SN65DSI86_IRQ_STATUS8 0xF8