Other Parts Discussed in Thread: DS80PCI402, DS80PCI402EVK

Hello,

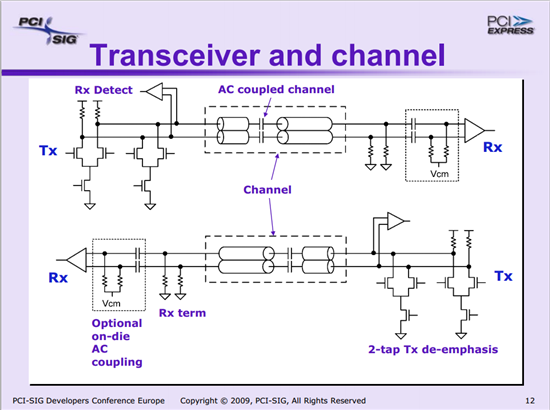

I have a Virtex 6 FPGA with a gen2 PCIe endpoint. The endpoint is muxed through a pericom PCIe mux PI3PCIE3422. The PCIe lanes are then re-driven through your DS80PCI402 on a PCIe card edge. There's approximately 10 inches of tracking from card edge through the re-driver and mux to the PCIe endpoint.

The endpoint is not appearing in the PC after booting up. These FPGAs are on mezzanine cards that work well in other systems, so the issue must be isolated the re-driver. I have tried different settings for RX termination, but using a scope I can see the TX signal from the FPGA is attenuated to almost nothing after going through the mux. If I power down the re-drivers the signal looks fine at the output of the mux, so it appears that the re-driver is killing the signal.

Is there any case where the re-driver inputs would effectively short out the inputs?

I see the common mode voltage is up around 2.2V for re-driver RX pins with termination forced to 50 ohm, is this to be expected?

I am operating the device in 3.3V mode.