Other Parts Discussed in Thread: DS90C383

I have designed a PCB which is intended to receive 4 Channel + 1 Clock LVDS video (640x480 24bpp), serialize the LVDS signal and transmit it over fiber optic cable and reverse the process and bring it back to 4+1 LVDS video. The source of the LVDS video is from a DS90C383 LVDS Transmitter. The DS90LV0411 is to serialize the LVDS into a single CML channel which is then sent to a CML 2x2 crosspoint switch, MAX3840. The crosspoint switch is used to drive two fiber optic transceivers (FTLF1319F1HTL and AFCT-5701APZ). The signal is then recieved on a second board (an exact copy of the board described above). One of the fiber optic transceiver is to drvie another CML 2x2 crosspoint switch which is then received by the DS90LV0412 which is supposed to transmit the original LVDS video. The destination device is a DS90C384 LVDS Receiver. I have attached my schematics for reference.

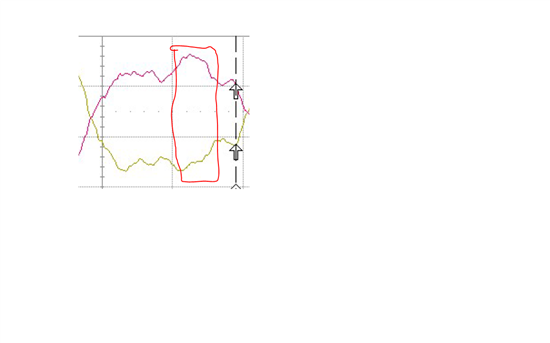

I am having an issue getting the video to display. When the system is outputting its startup menu, which is a black background with red text, it flashes quickly before disappearing. I probed the output of the LOCK pin on the DS90LV412 and noticed that I do not have a solid lock. The level will drop to 0 frequently. The issue gets worse once the system starts to transmit the video feed and the lock is very sporadic.

Prior to starting the project I spoke to the manufacturers of the major parts to ensure the interfaces would work and was told they should, but not guaranteed. I am unsure of the problem and what to look for when it comes to looking at the LVDS signal, beyond probing the lines and seeing that there is indeed a signal. I have access to a 4 channel Lecroy oscilloscope to probe the boards. Any help would be much appreciated. I can also provide the PCB layout if necessary.