[ DS90UB928 ] Delay from RIN to Valid Back Channel Communication

Hi,

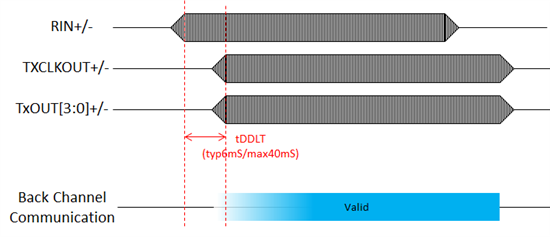

Do you have any numbers which describe the delay in between valid RIN and achieving valid back channel communication? Please see drawing below. Is it same delay that until having valid data output (tDDLT)?

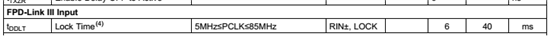

Also, is there any ways to calculate this Lock Time more accurately as per PCLK frequency? My customer would like to enable the back channel communication as soon as link is recovered.