Hello I'm facing a signal distortion in my i2c chain:

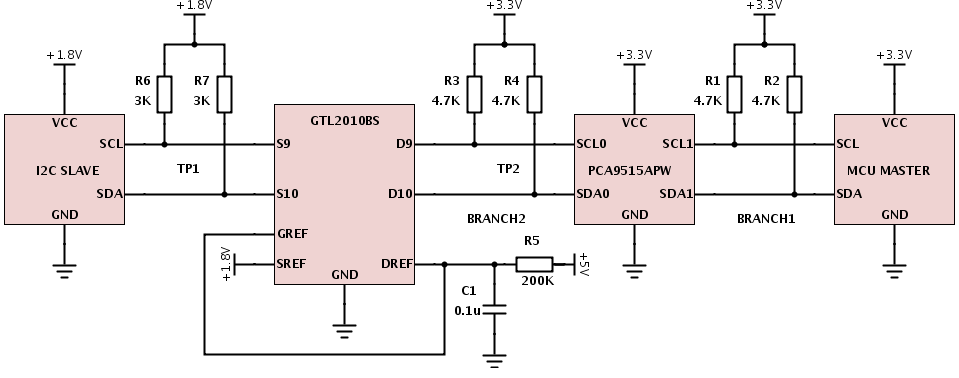

PCA9515 is used to split large i2c tree into several branches. The branch2 also uses level translator GTL2010BS to work with 1.8V levels.

The branch1 works well: i can address and read-write to devices, and oscillograms are clean (counting 0.5V low levels from PCA). But when I try to read from I2C SLAVE in a branch2 I get a acknowledge failure on byte send right after correct address transfer.

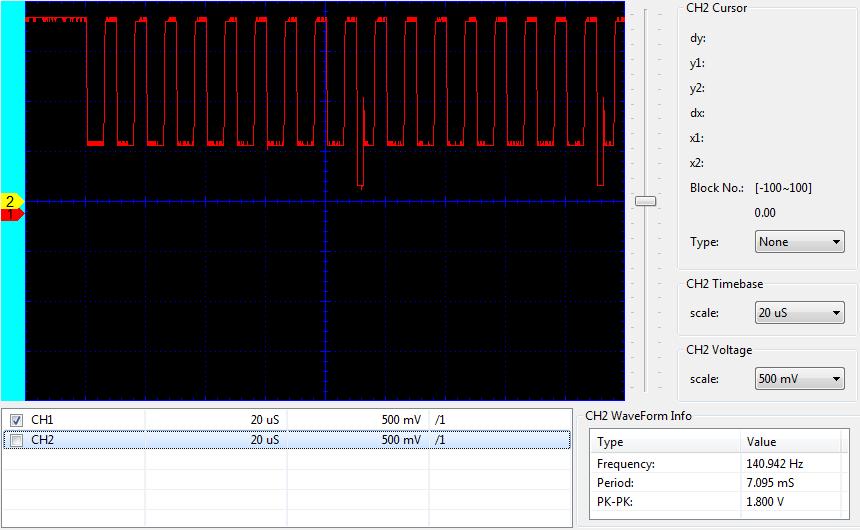

The oscillogram from TP1 (TP2 is the same) give a clue (red-scl, yellow-sda, I2C speed 100k, address then byte1):

After an address receive I2C SLAVE gives an ACK on sda line and right after ACK deassertion we can see a spike on SCL line:

This spike is interpted by I2C slave as a next SCL clock pulse, so slave shifts a data bit on in and the next transactions are shifted by one bit. The next ACK (on data byte transfer) arises one SCL cycle before it needs to - I2C MASTER doesn't see it on a real place and returns an ACK error.

If I ommit a PCA9515 from I2C chain (shorting BRANCH2 to BRANCH1) - the BRANCH2 starts to work.

Howhever I want to make a buffer work correct. What is a nature of these SCL spikes (they are following aright after I2C slave pulls SDA to real zero), is it the process of switcing SDA gate from output to input inside PCA9515 when the slave answeres, but why the SCL reacts on it? How can this spike can be filtered: may be a series resistors in a SCL and SDA lines (making pull-ups stronger wont help)?

Best Regards, Konstantin.