E2E Team,

I have a customer that is interested in using the TPD3E001 device in their design. They have some questions regarding implementing this device on some of their USB connections on their products.

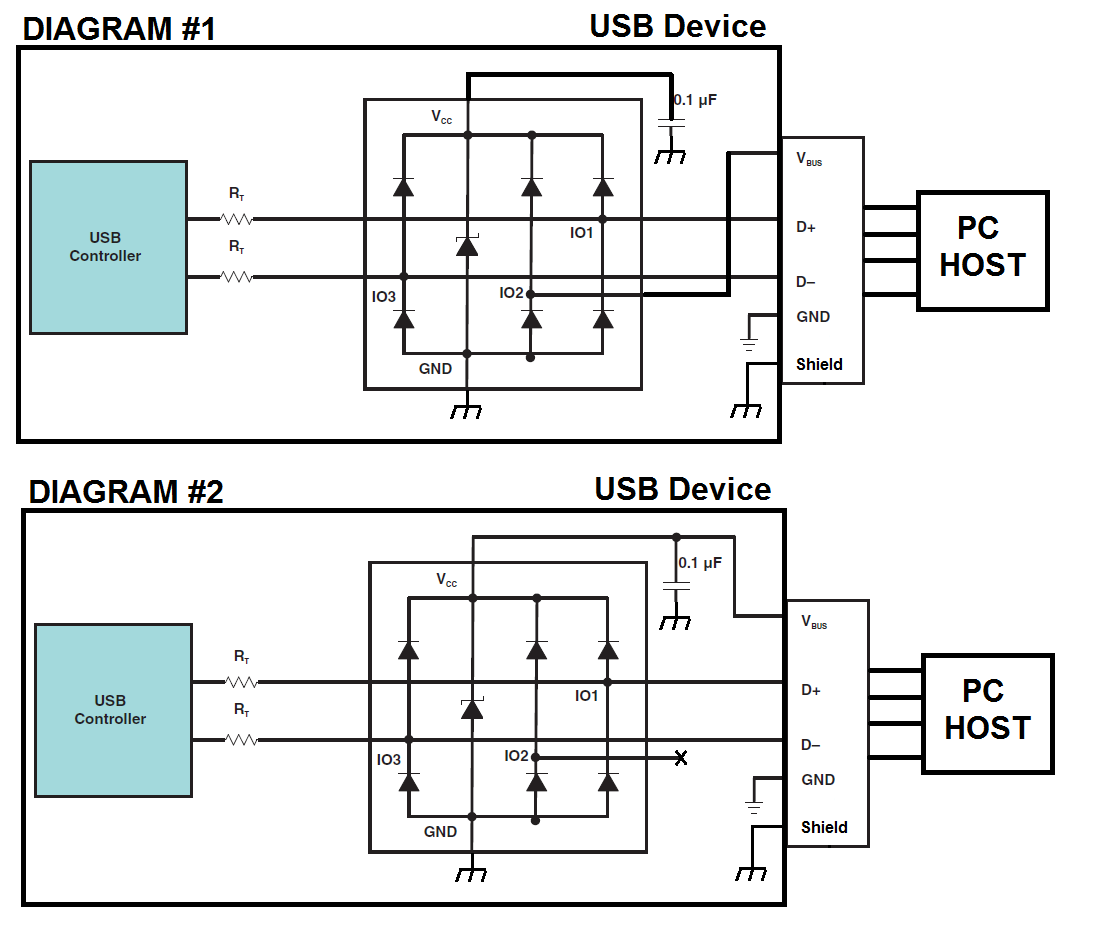

- Are both diagrams valid connection schemes, with the difference being #1 allows a 10V swing on the signals and #2 allows a Vbus + Vf swing? Or does either of the connection schemes not provide full ESD protection?

- Is the Vbus pin protected from ESD in both configurations, or only in #1?

- Should the ground of the TPD3E001 and the 0.1uF cap be connected to Earth Ground or Signal Ground? Does it make a difference if it’s a battery powered device (remote control) vs a dc adapter powered device?

- Is it appropriate to connect Vcc to Vbus if the PC is supplying Vbus? We don’t have any appropriate 5V rail in our device to alternatively connect it to.

- If we want to protect the D+, D- and Vbus pins from ESD, what would the recommended connections be with our device?

Thanks!