Other Parts Discussed in Thread: DS90C032, DS90C031, DS90C3201, SN65LVDS348, DS91M040

Hello,

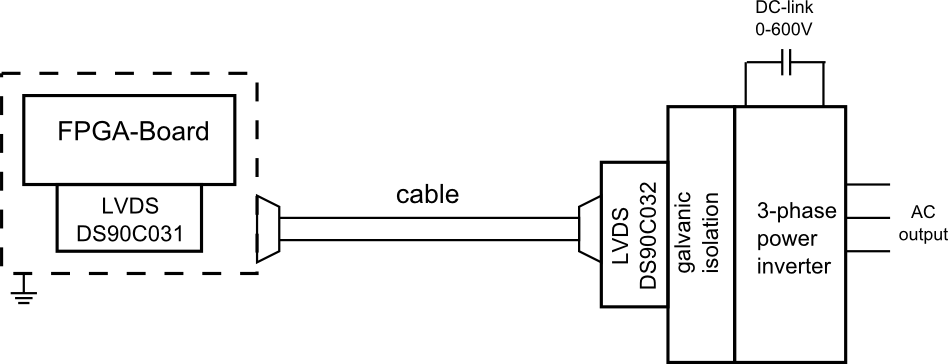

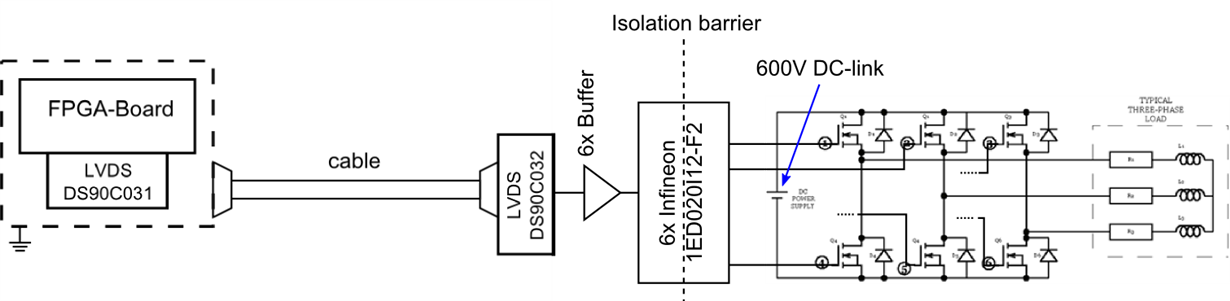

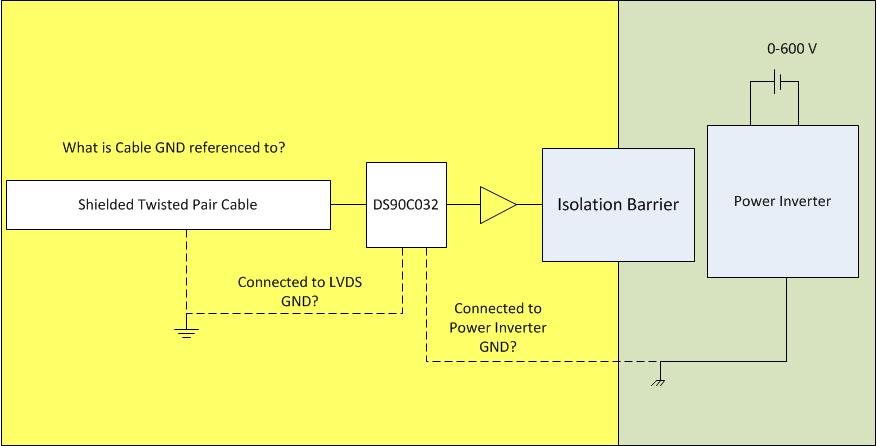

we are using the DS90C031 / DS90C032 Driver/Receiver to drive a three phase power inverter (600V@50A ~30kW) from a custom FPGA-Board. The cable is shielded, twisted pair and about 2m long. The power inverter uses SiC MOSFETs which are switching very fast (~100ns), so we have a high dV/dt. Thats why we have much noise on the cable that causes the Receivers to fail and sometimes they get destroyed. We added some common mode chokes at the inputs of the receivers. Now we got some more room but at 600V DC-link voltage the noise increases and the failures are back again. So what could be done that the receivers don't fail any more? Use another diff. signaling standard (e.g. PECL)? Other drivers/receivers with more common mode voltage tolerance?

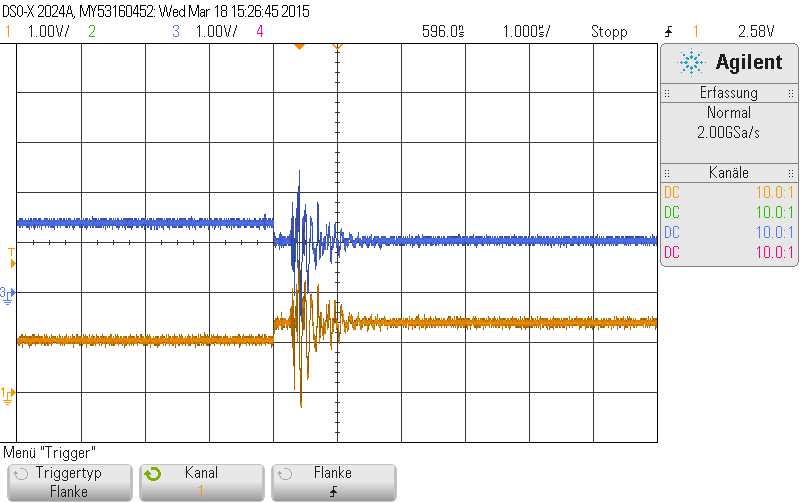

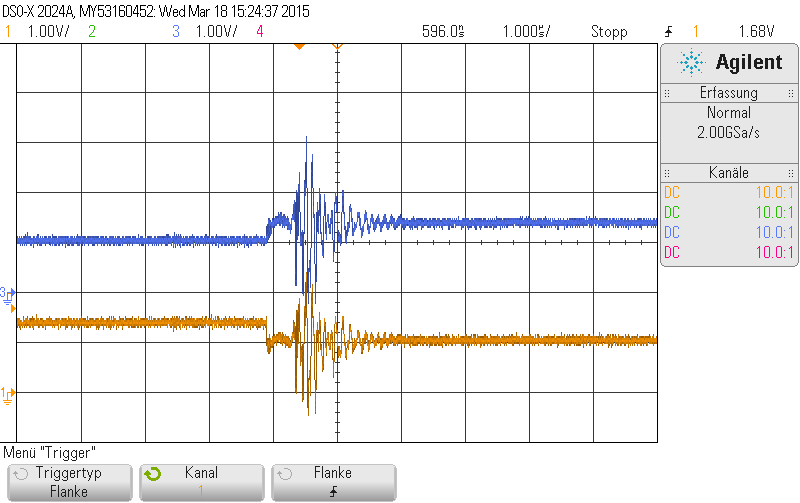

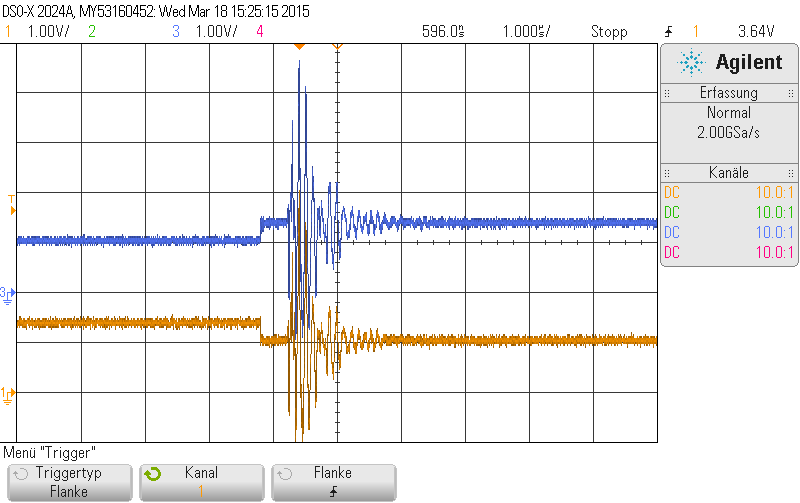

I added an overview of the setup and some oscillographs of the p-n LVDS wire. The high common mode noise could be seen on the plots which gets higher with increased DC-link voltage. I already found a thread that discusses this topic but unfortunately its closed without a visible result (http://e2e.ti.com/support/interface/high_speed_interface/f/138/t/402489).

LVDS p-n wire @ 100V DC-link voltage

LVDS p-n wire @ 200V DC-link voltage

LVDS p-n wire @ 300V DC-link voltage