Other Parts Discussed in Thread: TCA6416A

Hi Team,

Our customer are evaluating TCA6416A.

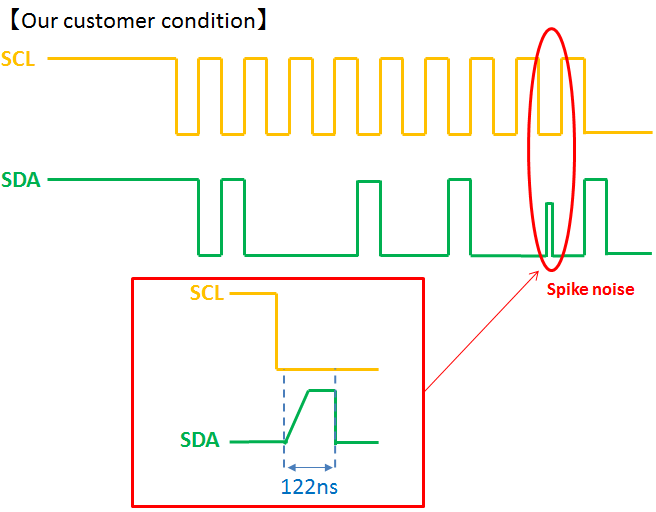

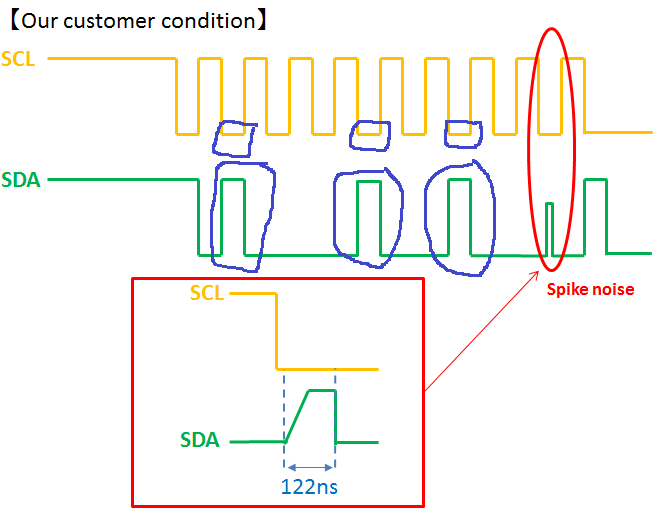

However, the spike noise occurs on the SDA line.

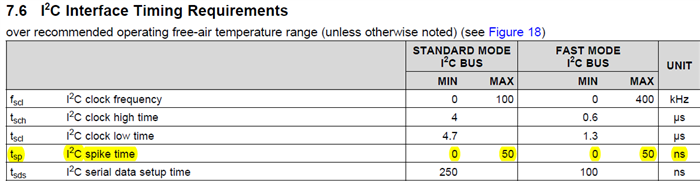

This noise time is more than the I2C spike time(50ns(max)).

Therefore, we would like to ask the following question ([Q1] and [Q2]).

----------

[Q1]

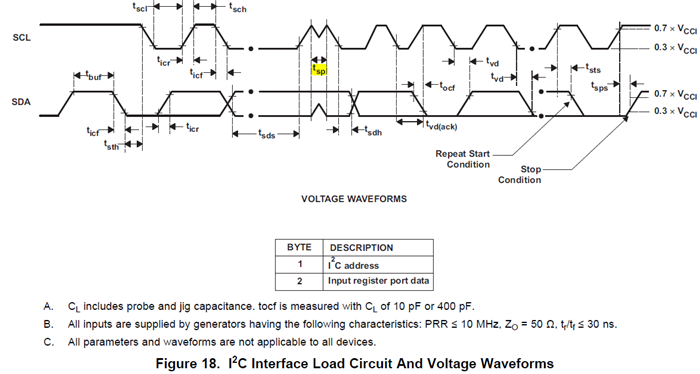

According to the Figure18 of datasheet, the spike noise is occurring when the SCL is High.

I’m understanding that this case is a communication error if the spike time is more than 50ns.

If the spike noise occurs when the SCL is Low, does the communication error occur?

-----------

[Q2]

Why does this noise occur?

Could you please let us know if you have the workaround?

----------

If you contact to below my e-mail address or let me know your e-mail address,

I can send the customer information.

I’m looking forward to hearing from you.

[my e-mail address]

Regards,

Kanemaru