Other Parts Discussed in Thread: SN65DSI86

Hello,

We got SN65DSI86 (-Q1 version for prototyping) on a test board. Did not hookup I2C (as this was intended), and wanted to configure it strictly over DSI channel.

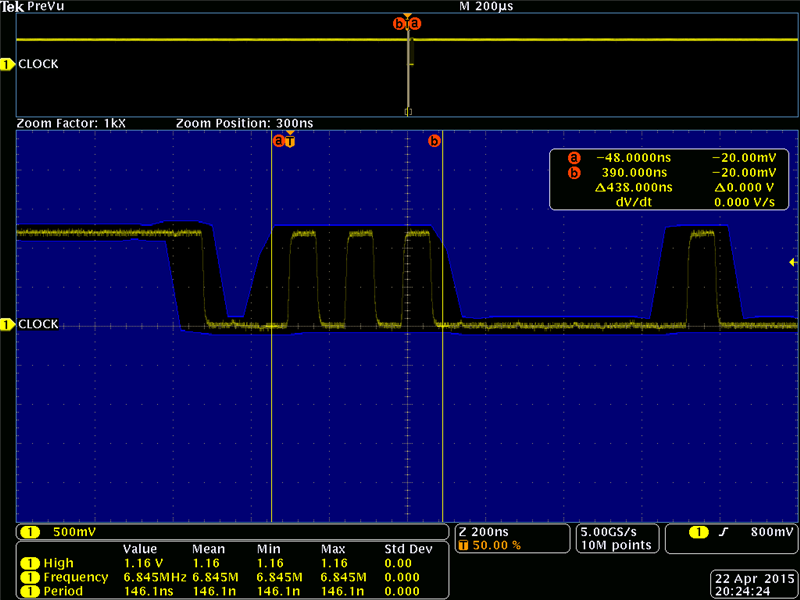

At first, the board was strapped for 27MHz crystal - and watching DSIA_RX0 with a scope gives the following:

pic1: zoomed into transmission, to see bit time. 146ns.

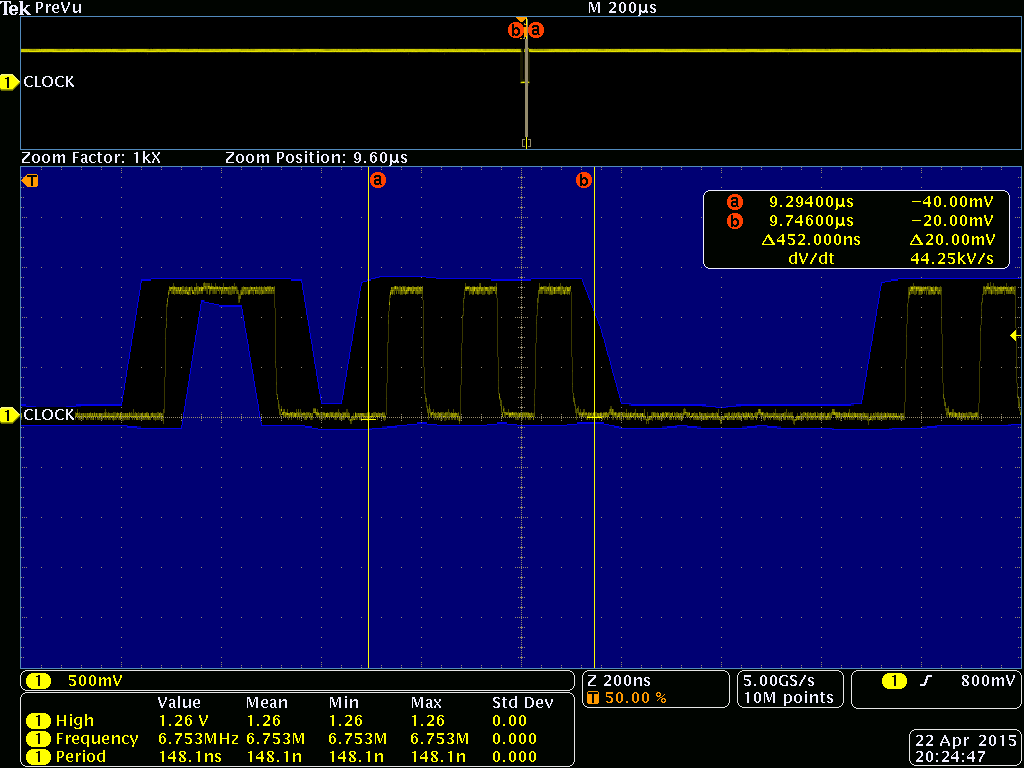

pic2: zoomed into reply from DSI86, to see bit time. 148ns.

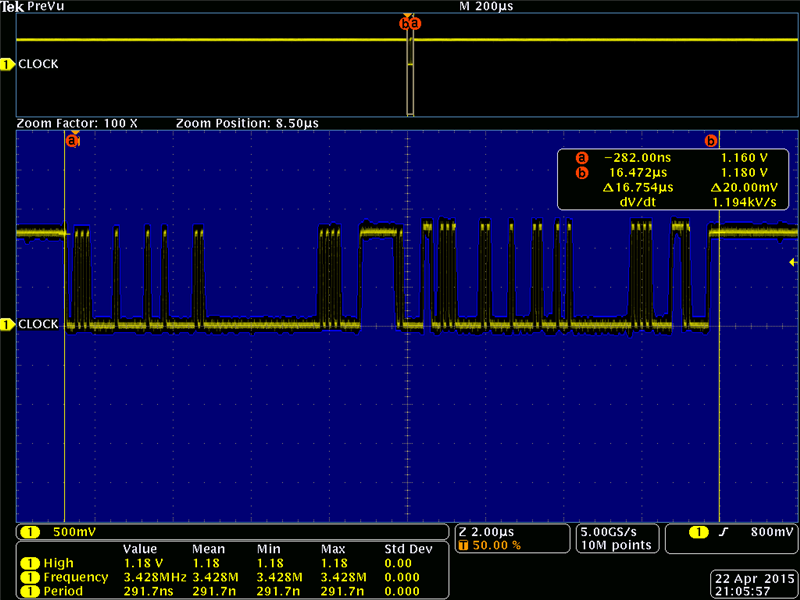

However, the DSI host is not seeing reply - It is actually seeing DSI return packet 0x11, I think, but the data fifo returns empty. Below pic is entire exchange.

So, the question is:

Is this working? Is the problem on my DSI host end?

The transaction looks ok, is 2ns difference in bit width going to affect reception?

On the DSI host I don't have a lot of granularity for setting transmission timing - there is 'LPTIME' parameter which is currently set to '6' in order to get the 146ns-wide bits. Setting it to 5 gets me 124ns wide bits, and 7 gives me 167ns.

If this 2ns @27MHz timing is not accurate enough, is there something I can blindly write into the DSI86 registers (over DSI) to switch it into clocking from DSIACLK or similar? Or is there something else I'm misisng for the setup.

The Short read (0x24) and its arguments are correct (well, I'm reading register 00, and expecting to get back 0x20).

This is the first command I'm sending to DSI86, after deasserting Enable pin. Communication is in LP mode, using DSIA_RX0.

edit: After, the board got strapped for 19.2MHz refclk, and with that, the bit width in rx/tx is even more different, so we'll probably go back to 27MHz unless instructed otherwise. The DSI host is running from 19.2MHz refclk.