I have some general questions on LVDS design and have been referring to the following guides:

http://www.ti.com.cn/cn/lit/an/slla014a/slla014a.pdf

http://www.ti.com/lit/ml/snla187/snla187.pdf

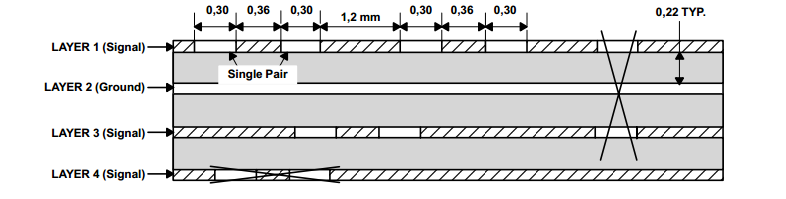

1) On my board I will have 6 layers, if I run a trace on a middle layer then do I need to have ground on layer above and below the trace? I am assuming I do based on the figure above.

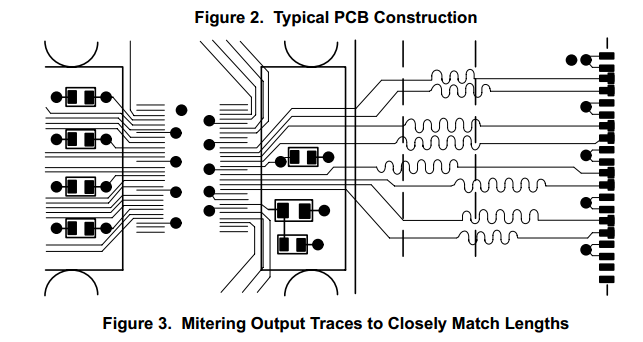

2) It's my understanding that the spacing between traces in a pair should be less that twice the width of a trace, however the diagram below which shows mitering traces to match length visually implies that the spacing is much larger than twice the width. Is the spacing between the traces critical?

Thanks!

,Nabeel