I'm trying to get two of my microcontrollers to communicate with each other over RS485, and I'm using a SN65HVD1782DR as the transceiver. I have the /RE pin tied to ground on each PCB. Each microcontroller will raise the DE line whenever it wants to transmit data.

I have a couple of problems. The first problem might be the cause of the second one, but I'll do my best to explain what's happening.

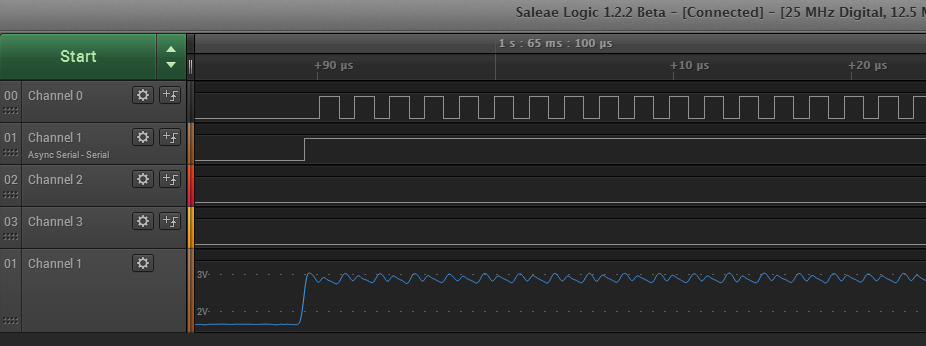

When I send my Modbus packet to the slave and look at the state of the RS485+ and - lines with my logic analyzer, I always end up with a framing error as it's sending the last byte, which is the last byte of the CRC. My pseudocode for my RS485 write function looks like this:

- wait for DE to go low

- set DE high

- send packet

- set DE low

I noticed a couple of interesting things during debugging. First, if I change my code to just send an endless stream of bytes, I never get a framing error. Secondly, if I put a 1ms delay between the end of sending a packet and setting DE low and send the previously-failed packet, I don't get a framing error.

With the second hack in place, I was able to send data to my slave, and the slave received and processed it. Now the problem is that it sends data back, but the master never receives it.

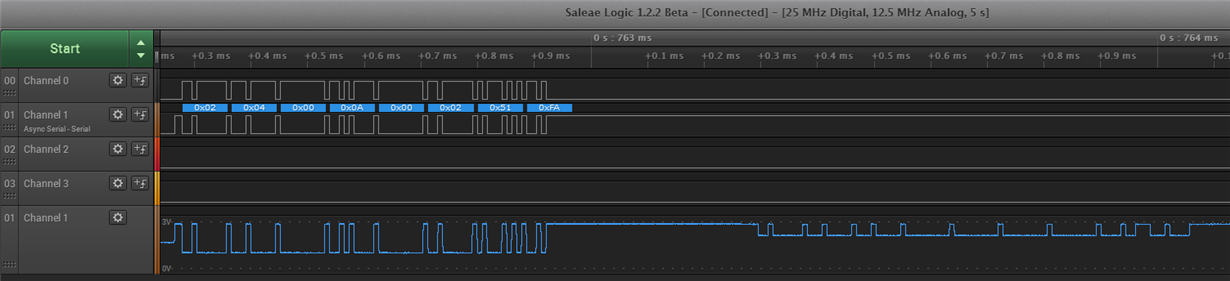

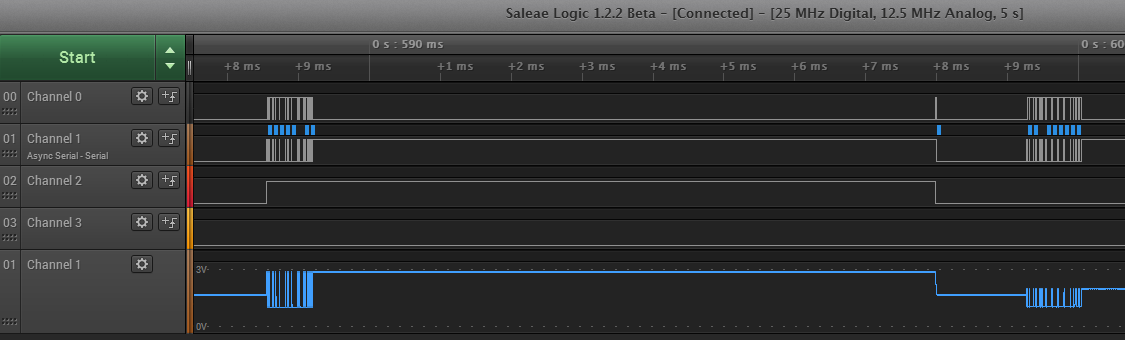

I logged data with my logic analyzer for the round-trip command, where the master sends a packet and the slave sends a response packet back. Here's what the transaction looks like:

So clearly there is some signal-level issue here. The master can send data, but the slave can't respond. Well, it looks like the slave does respond, but the signal levels are incorrect.

Is there anything else special that I need to do when using these particular RS485 transceiver? I don't see anything else in the datasheet that strikes me as important.