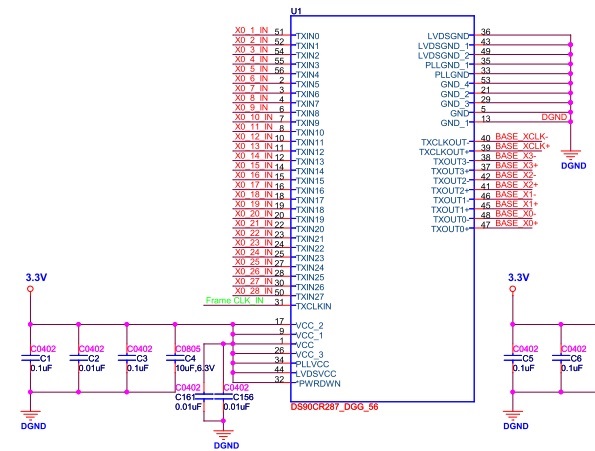

Other Parts Discussed in Thread: DS90CR287

Dear sir:

I found there's abnormal output issue when input and clock signals are off. Here's 3 pictures I got from power up, data in and data off of the TXout0+

Power up step picture, TXout0+ is correct with no clock/ data input

signal (Txout0+) on with clock input picture which is correct waveform

signal (Txout0+) with clock/ data input off picture, there's unknown signal output even without clock/ data inputs.

I have also checked the Txclkout+ and all other LVDS pairs and got similar unknown waveforms as well. Are these waveforms reasonable?

Why we have these waves after parallel clock/ data inputs?

Thank you!

Brian