Other Parts Discussed in Thread: TLK110

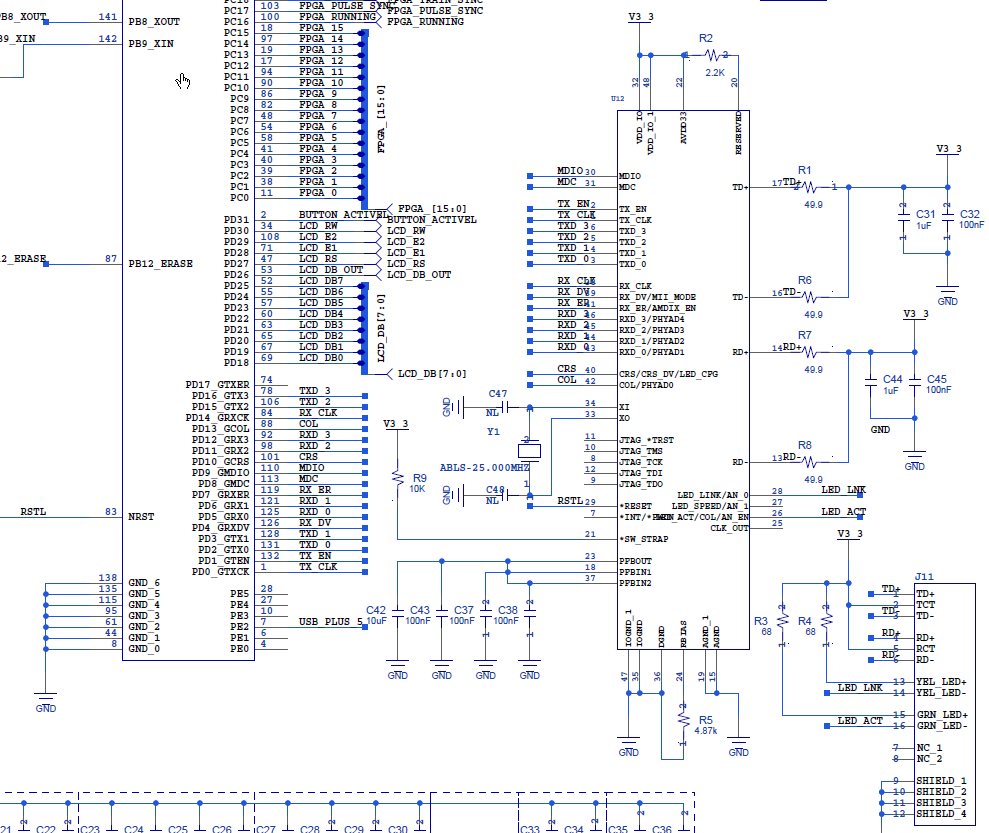

I have a board with the TLK110 wired as per the attached schematic. (The circuit on the left is an ATMEL ATSAM4E) J11 contains magnetics as well as the connector.

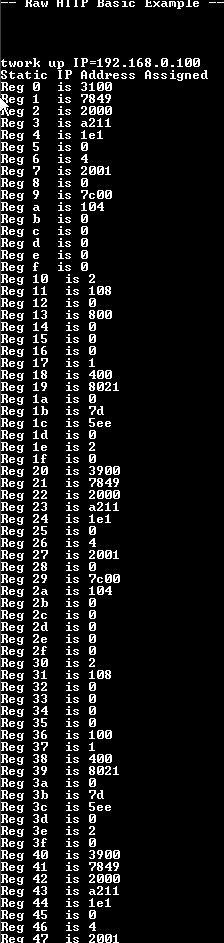

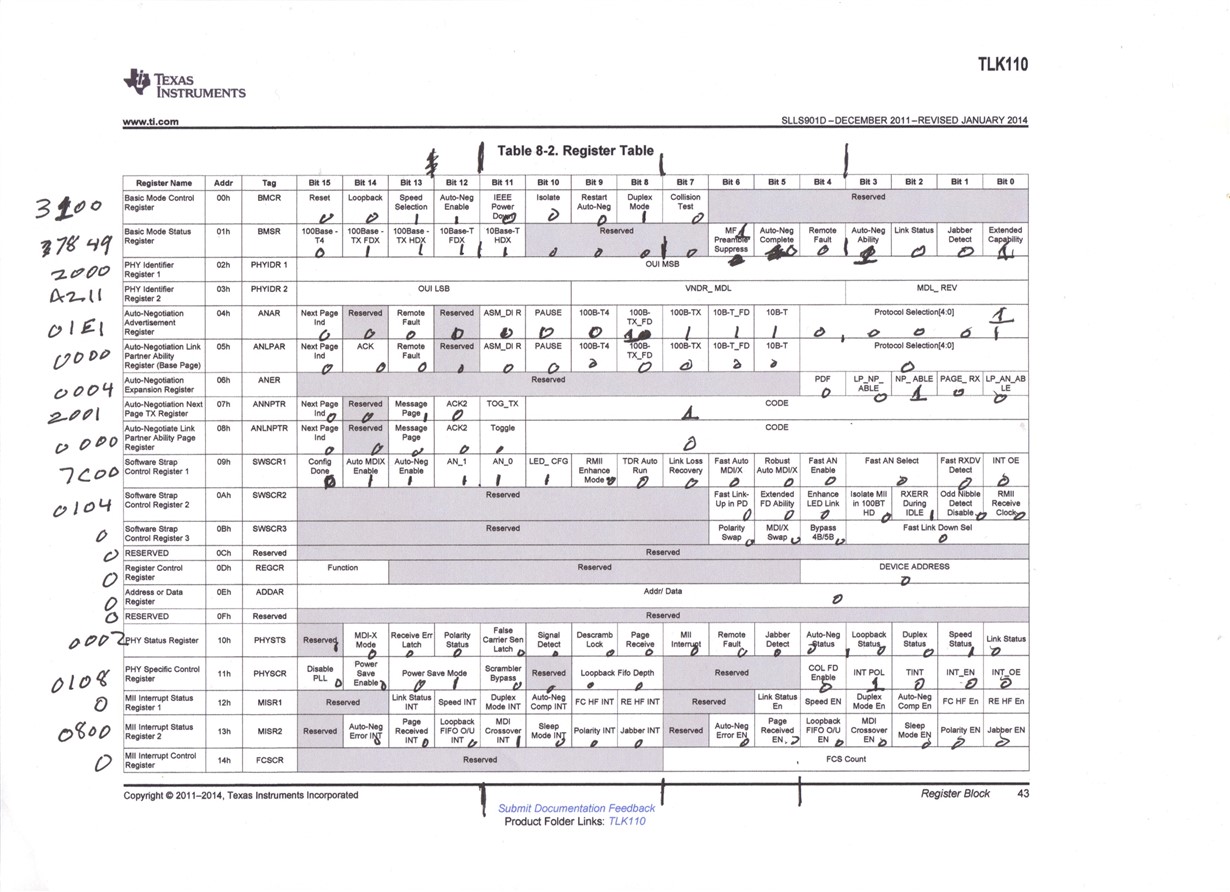

The problem is that it does not negotiate or establish a link. when a cable is connected from J11 to either the Ethernet connector on my PC or a router. Some other observations:

1. None of the LED's on the connector/ magnetics go on

2. There is 3.3 V on pin 48. It's power-on rise-time is ~ 2ms

3. There is 1.5 V on PFBOUT

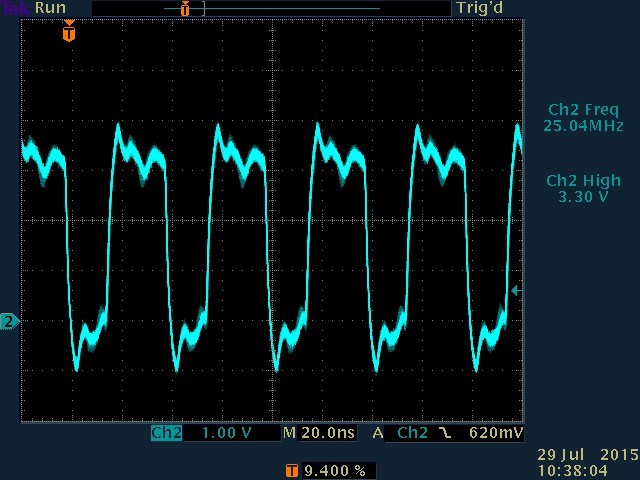

4. There is 25 MHz oscillations on X1 and clock out

5. The RESET pin is connected to a normally open switch to ground. It sits at 3.3 V until the button is depressed when it goes to ground and then returns to 3.3V if the button is released. Doing this doesn't seem to effect the TL!K!10. It's as if it is continually in reset.

6 On the off-chance that the chip was defective or damaged, I replaced it and nothing changed.