Dear Sir,

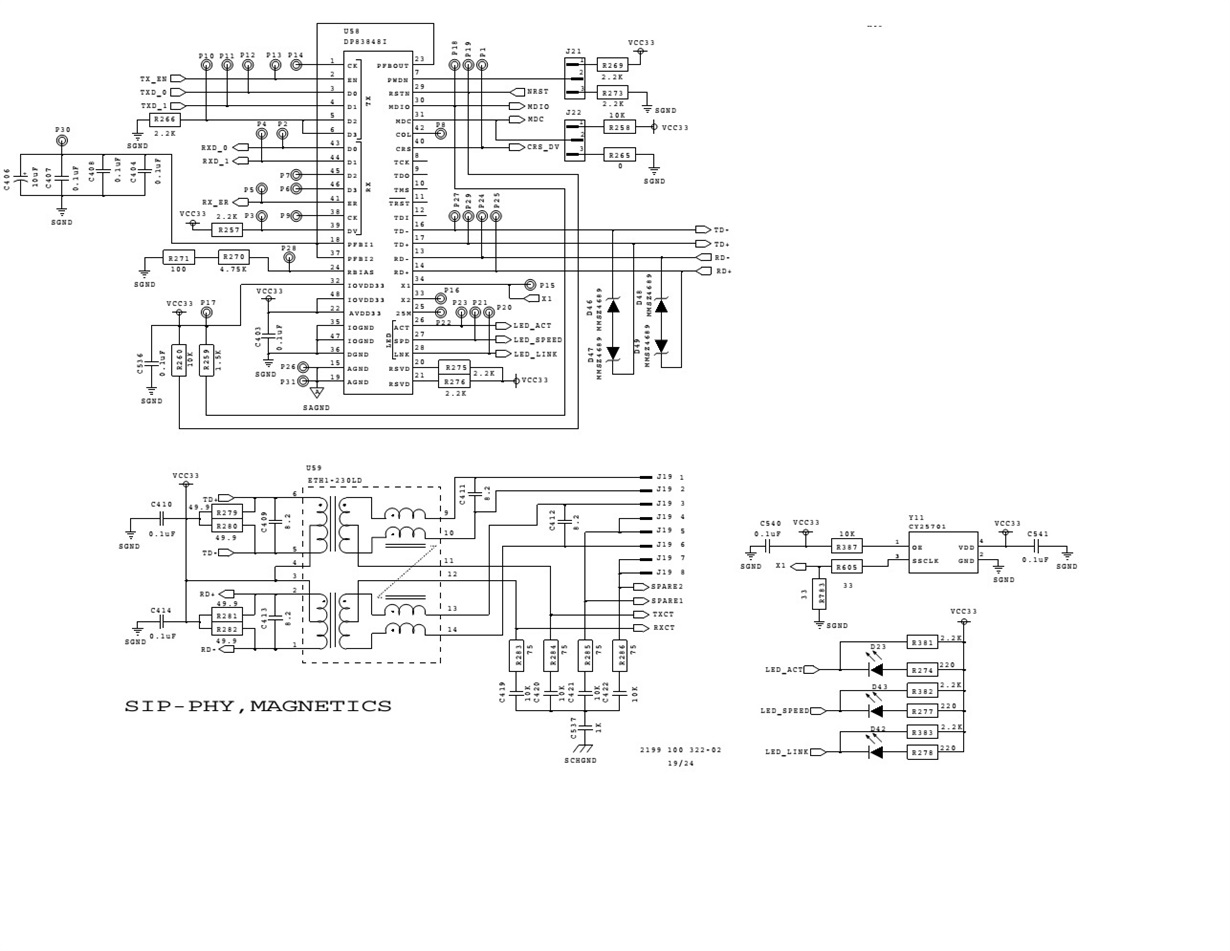

We are using DP83848I PHY please find the attached SD, when the phy is powered on firts time

the link negotiates to 100Mbps full duplex and I'm able to ping the PC.

If I unplug and replug the cable at some instance( for 3rd or 4th time) the phy negotiates to 100Mbps half duplex and further remains to 100Mbps half duplex inspite of unpluging and replugging of cable.

If I provide a manual reset to the IC at this time, the phy negotitates back to 100Mbps full duplex and it starts pinging.

During half duplex mode on the pc side Im able recive arp packets, but whatever pc is sending the phy is not receiving the data.

If I run the command ifconfig eth0 down and ifconfig eth0 up

it says eth0 duplicate address detected.

How to resolve this issue. Mean while I'm trying to read the registers via MDC/MDIO.