Other Parts Discussed in Thread: SN65MLVD206, AM3359, DS92LV16

Hi all.

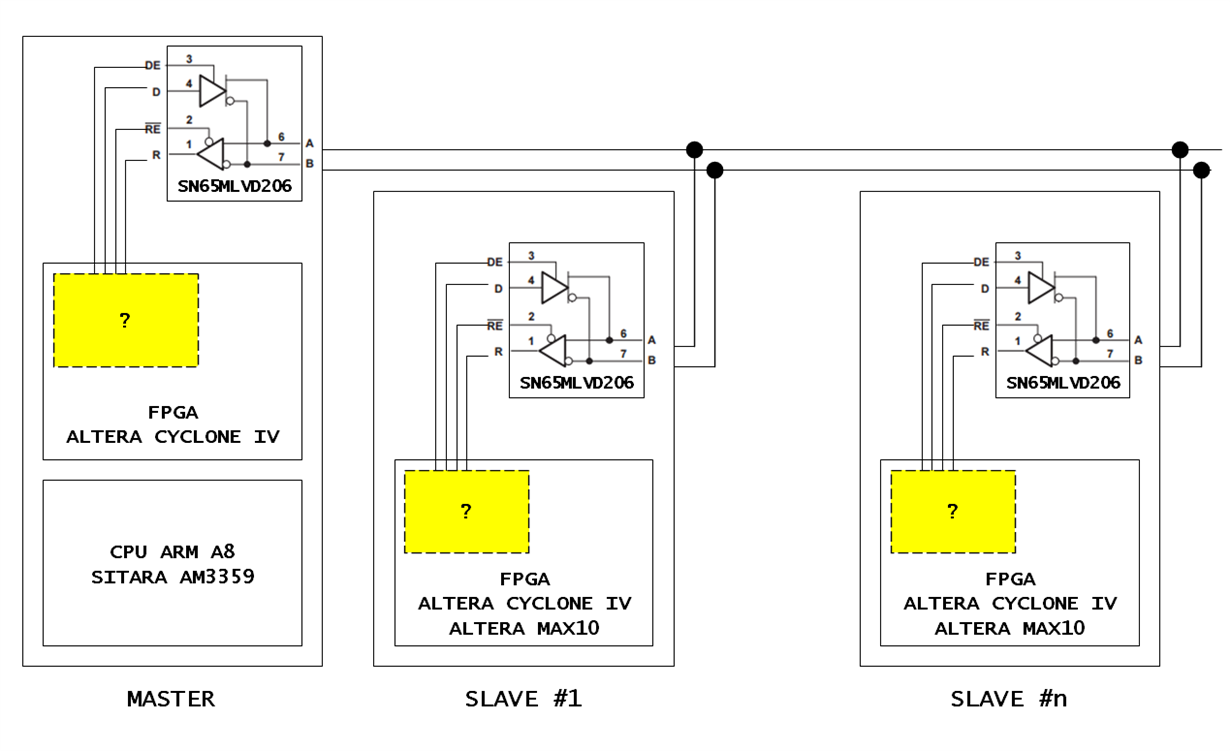

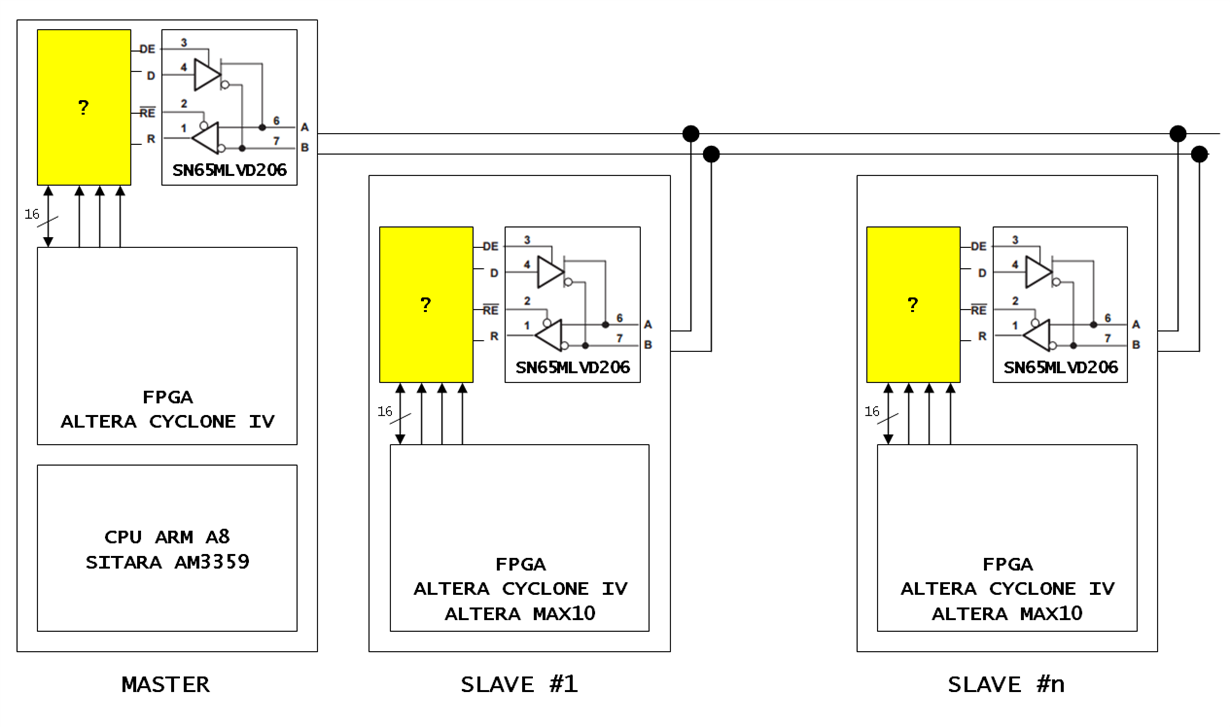

I'm developing an industrial FPGA interconnect back plane. I need to communicate over a single differential lane, with a master that initiates a request and one out of several slaves that responds. Serial data rate should be greater than 150 Mbps (16 bit parallel data, at least 8/10 words per microsecond bursted on bus)

I want to use SN65MLVD206 MLVDS transceivers, because they meet the target speed and are the best pick for noisy environment.

Master is based on Altera Cyclone IV and Sitara AM3359 CPU; slaves have one Altera FPGA (low cost, maybe MAX10 family).

Question is: I don't know nothing about hot to serialize/de-serialize the parallel data coming from FPGA:

- Altera IP cores use embedded LDVS transceiver inside FPGA, and I can't drive OE of SN65MLVDS206 to address half duplex communication;

- Altera LVDS communication is available only in "full featured" devices; cheap MAX10 family doesn't support serdes IP cores.

Do you have any suggestion as kick-start (demoboards, reference designs, etc...)?

I think I could spend extra money and use ab serdes IC, between MLVDS transceiver and FPGA (yellow box in figure below):

I can't find a suitable IC from broad TI portfolio of serdes devices, because:

- no clock distribution lane is available

- only one lane for data (and embedded clock): I think this could allow half duplex communication only.

- serdes devices don't support external PHY, so MLVDS is not possible.

Hints?