Hello!

For us, please contact the LVDS waveform issue

< check way >

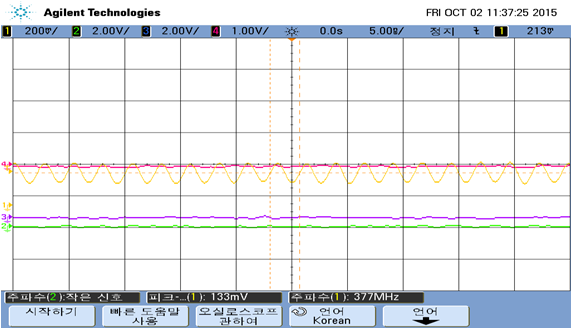

1) When passing the MIPI Video Signal in Black pattern.

2) The initials Write of the SN65DSI84 IC

< result >

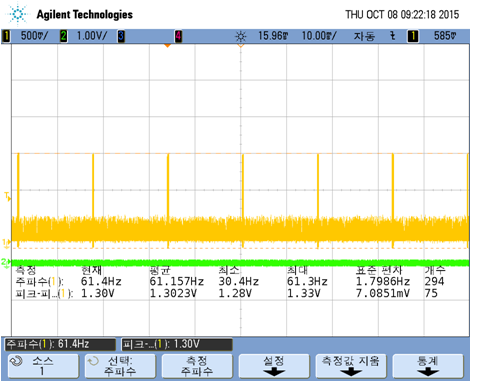

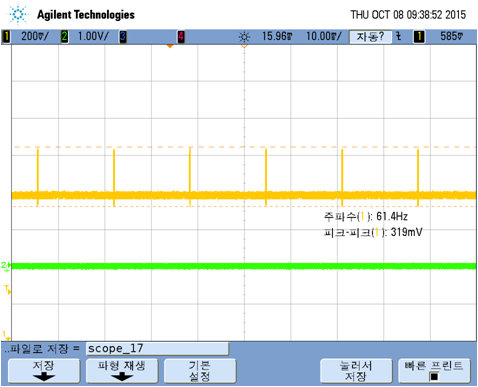

LVDS waveform of A_Y0P / N line of problems that Data is output per 60Hz.

< Reference materials >

1) MIPI - Black Pattern

2) LVDS - A_Y0_P line

please answer about my question.