Other Parts Discussed in Thread: TLK105L

We are using the TLK105L part on a design with an IMX6 processor running Linux with Freescale’s provided generic 802.3 driver. Recent ESD testing with an unshielded cable has shown a previously undiscovered problem where the link will go down and not come back up again. This happens at Air ESD levels as low as +6kV. Only happens at + for some reason. No discharge actually takes place, just having the static field present near the cable causes the problem to manifest. I have direct register access and I was able to identify 2 failure modes.

- Phy gets stuck in MII mode instead of RMII mode. Register 0x17 is reads 0x0061 when working properly and 0x0041 after the ESD event. Writing the register back to 0x0061 has no effect. Toggling the hardware reset line causes this register to come back to 0x0061. My best guess is the PHY is resetting and not sensing the MII_MODE pin properly during power-up. This operation is not desirable, but at least its detectable and it can be remedied with software polling register 0x17 and toggling the reset line. Some register setup is also required after the reset, I can share that detail if you like.

- Phy gets locked continually changing between MDI and MDI-X mode. Read register 0x13 and see it’s a 0x0800 every time its read. It’s supposed to clear to zero after a read, but this interrupt flag is constantly set in the fault condition. This is the same result as if there is no cable connected, so it may not mean anything. Either way, the link is down and toggling the reset line does NOT bring it back. The PHY has not been damaged as far as I can tell since a reboot of the entire system does bring it back.

Things I tried that didn’t help:- Setting the bit that restarts Auto-negotiation.

- Setting register 0x17 to 0x0041 and then back to 0x0061 to hopefully re-init the RMII link.

- Disabling the Auto MDI/MDI-X and manually setting it one way or the other.

- Writing register 0x1F to 0x0040. It’s a reserved bit but I see it set sometimes and not others.

- Writing register 0x1F to either 0x8000 or 0x4000 to accomplish internal resets.

I made some quick screenshots of the schematic and layout since those are usually the first questions. The layout just shows the top layer, but it’s a 10 layer PCB. The connector is an M12 circular industrial Ethernet. As you can see there is a large gap between the plane where the connector is at and the plane the PHY references. At the moment we are trying to make software changes only since the design is frozen. It’s totally fine if the PHY resets and relinks. The trouble is when it gets stuck and requires an entire system reboot to come out of it. It’s really strange that toggling the PHY reset line does not accomplish the same thing as a system reboot in the case of the 2nd failure mode.

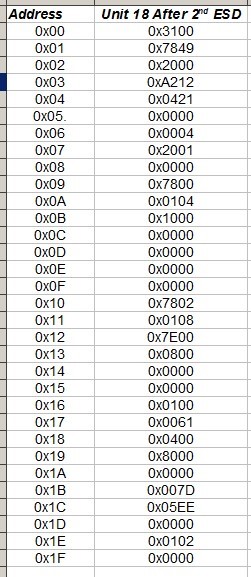

Here are the first 32 registers after the ESD event causes it to get into the 2nd failure mode. I did note some of the reserved registers were not at the default state, if that means anything.

Any clues or things to try would be greatly appreciated. Thanks for your help.