Other Parts Discussed in Thread: DS90CF383B, DS90CF386, DS90CR218A, DS92LV2411

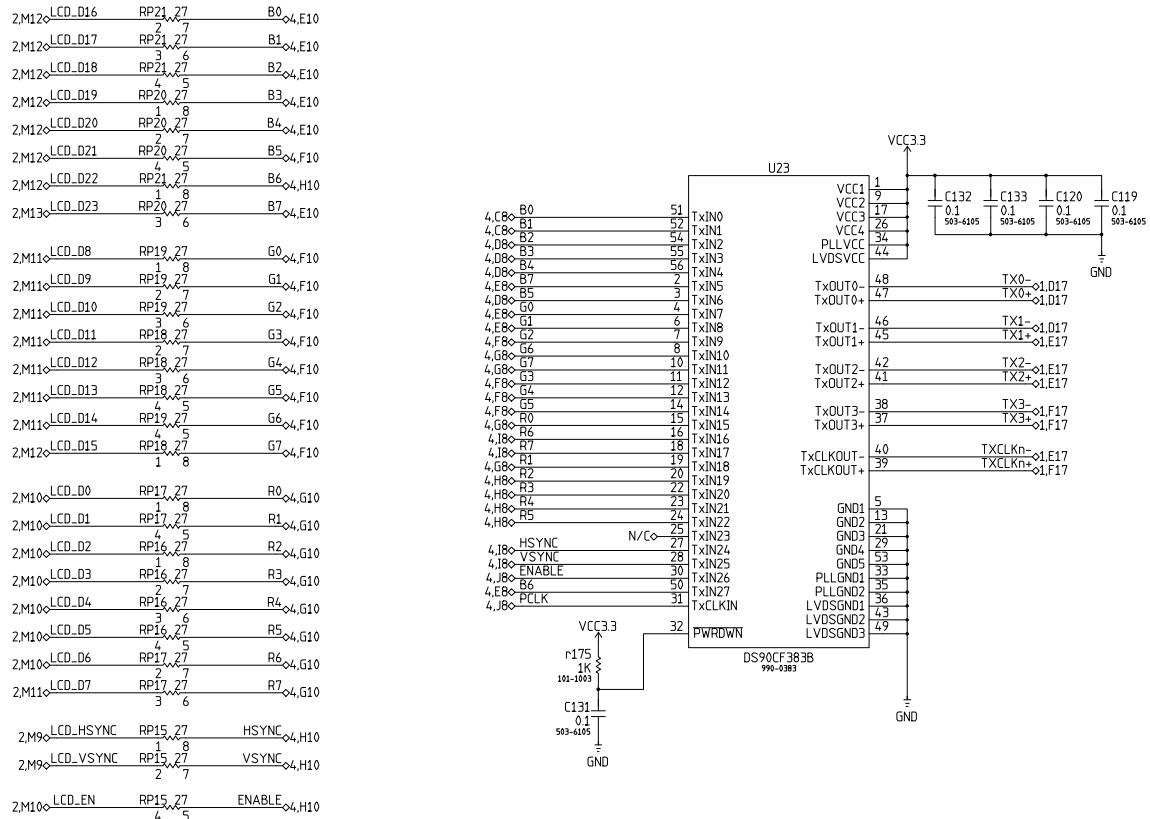

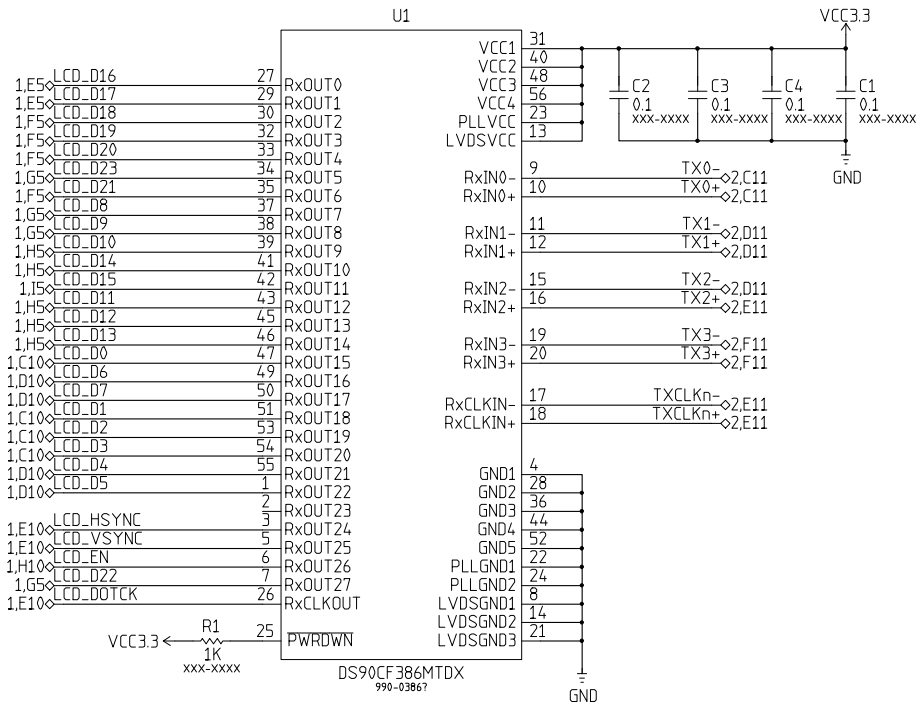

I have a product that was driving a display directly through an RGB type connection, the system architecture has changed requiring the use of LVDS across a cable (12" long) to the display. I am using a DS90CF383B LVDS Transmitter connected to a DS90CF386MTDX Receiver which I am attempting to run with a TxCLKIN at 19Mhz. What I see on the display is unrecognizable "moving fuzz".

To troubleshoot this I've confirmed that the cable pin out is correct between the two controllers. I noticed that while I'm inputting a Dot Clock (TxCLKIN) of 19MHz, I'm getting out a Dot Clock of 56MHz out of the receiver.... Additionally the TXCLK+/- signal appears to be running at 19MHz. I believe this differential clock should be an order of magnitude 7 times higher then my TxCLKIN to transmit all 24 bits of color data. It looks like the internal PLL is not locking for some reason.

Could someone provide me some with some assistance to help guide my debugging?

Thanks,

Mark

TX Schematic

RX Schematic