Other Parts Discussed in Thread: DP83620

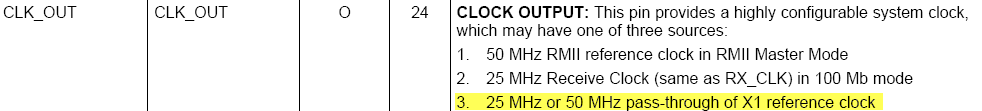

I am planning on using either a 25 MHz crystal or oscillator in RMII Master Mode. I need a 50 MHz clock output for the MAC of the microcontroller, 25 MHz or 50 MHz for an FPGA's clock, and 25 MHz for the microncontroller's main clock. From other posts I've read in the forum, it looks like the DP83620 will do what I want. But I would like someone to confirm that it will and there won't be any issues. It is my understanding that TX_CLK and RX_CLK will both output 50 MHz, which will work well for the FPGA and MAC. The data sheet shows the following info for CLK_OUT.

I didn't find any more information on the 25 MHz pass-through option in the data sheet, but from what I read in the forum it appears this is the default mode. Is that true? What happens to all three clocks when the RESET_N pin in pulled low, or any software resets are performed?

Thanks,

Greg