Other Parts Discussed in Thread: DS125DF410

Posted on behalf of another E2E user:

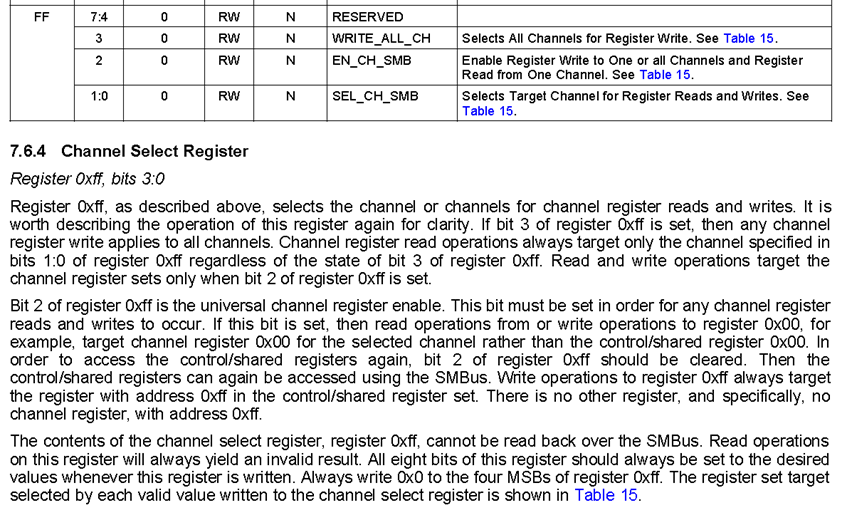

Questions regarding the DS125DF410 channel select register, Reg_0xFF:

- Does "set" bit 3 of register 0xFF mean "set it to 1"?

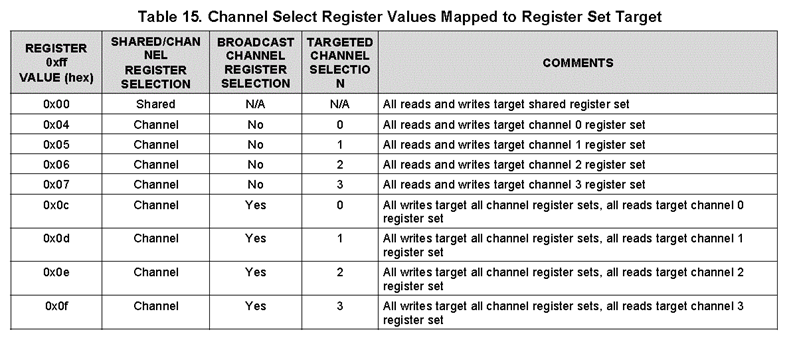

- In order to reduce the number of I2C (SMBus) writes, can we implement "Write to all channels / Read from channel 0" by setting Reg_0xFF=0x0C?

- Is there any sequence required for setting the channel select register (Reg_0xFF)? In other words, must I first select a channel, and then enable broadcast mode, or vice versa, or the sequence doesn't matter?