Other Parts Discussed in Thread: LMH1983, LMH1981

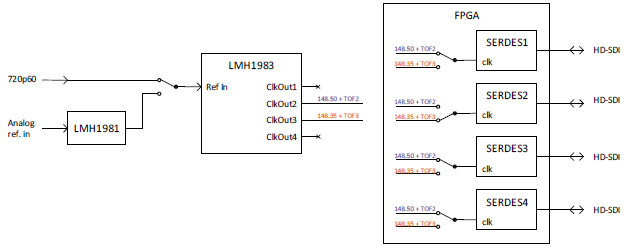

When I genlock the LMH1983 to a 720p60 reference signal, every 1000 frames (about 16.66ms) the clock period of the 148.35MHz clock has a clock period that is too short, sometimes more than 1ns too short. As a result sometimes the PLL in the FPGA loses its lock.

Is there anything I can do in the register settings to prevent these narrow clocks?

Regards,

Henri Faber