Other Parts Discussed in Thread: HD3SS460

Hi Team,

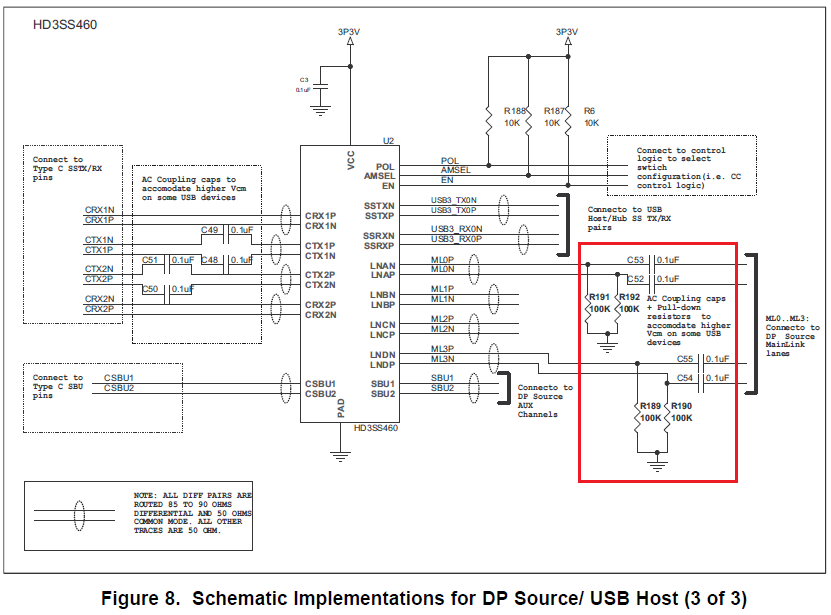

Does the following Figure 8. shows "AC Coupling cap + Pull-down resistor" is required for ML0P/N and ML3P/N only?

I believe it is just omitted and "AC Coupling cap + Pull-down resistor" is also required for ML1P/N and ML2P/N.

Is my understanding correct?

I would like to confirm just in case.

Best Regards,

Yaita / Japan disty