Hi

I have used SN65LVDT386DGGR as a receiver from multiple planks and that high speed signals routed to FPGA from the output of same chip.

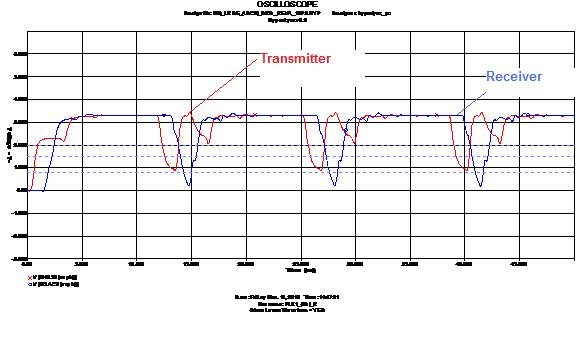

Signals are operated in 75MHz and while I am tried to simulate the signals I have seen the signal from the driver side and receiver side waveform was not an expected pattern.

I have given 50% duty cycle in the simulator.I have used hyperlynx 9.2 version for the analysis.

I want to know ibis i chose is correct or not.

I have attached the waveform and ibis model.

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/138/1373.0317.SN65LVDT386DGG.7z